两位加减法电路设计与数码管显示:补码与原码应用

需积分: 0 133 浏览量

更新于2024-08-05

收藏 946KB PDF 举报

在本篇关于"简单组合逻辑电路的设计1"的文章中,主要探讨了两位数字电路的设计,特别是针对加法和减法运算。首先,实验目标强调了理解小规模数字集成电路组合逻辑电路的分析和设计方法,以及掌握补码的概念和在减法运算中的应用。

实验内容具体包括:

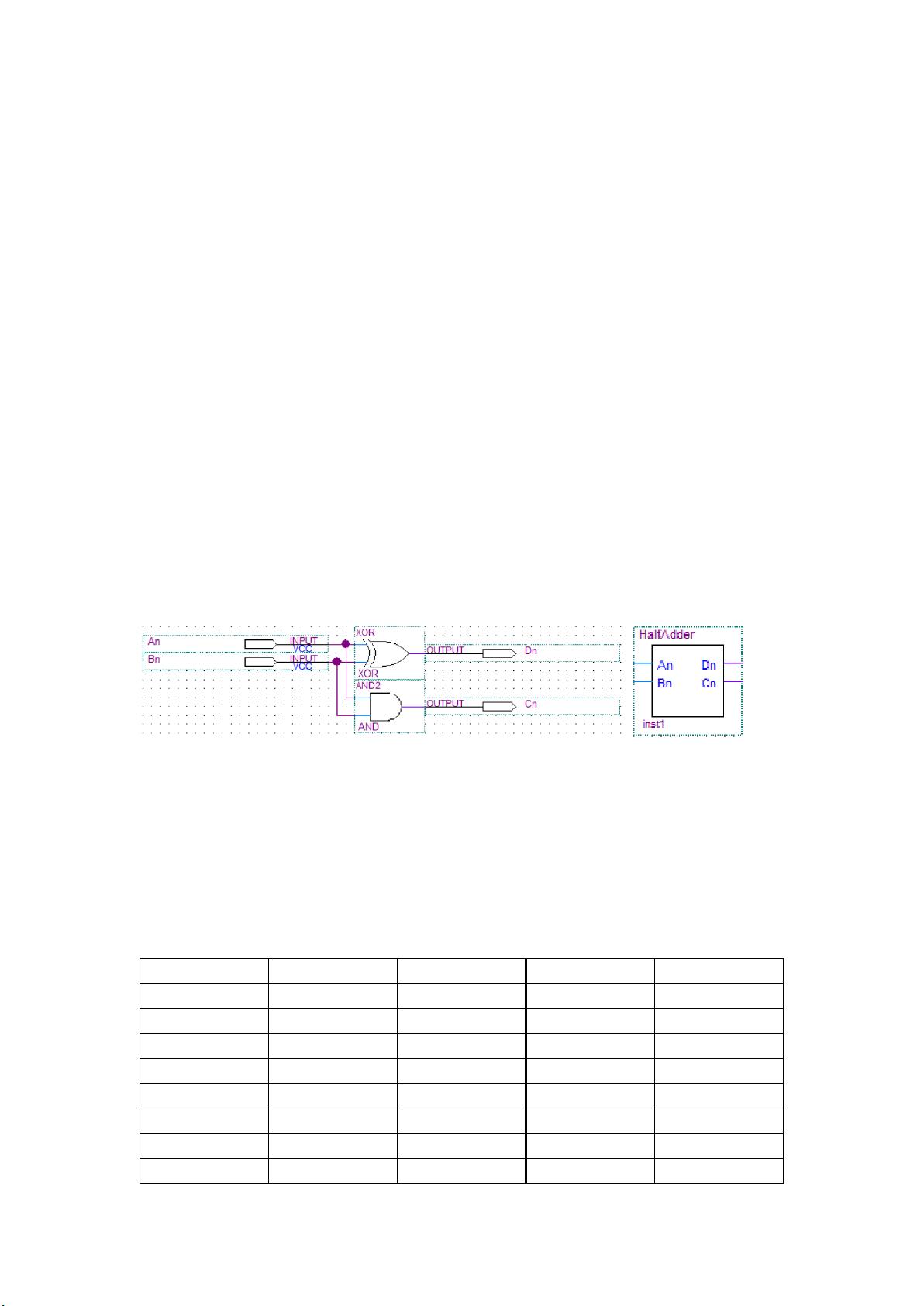

1. 设计并实现两位加法运算电路,要求能通过数码管显示加数、被加数和最终的和。这涉及到基础的二进制加法,通过半加器和全加器电路的级联来完成,全加器的逻辑表达式考虑了与非门的优势,简化了电路结构。

2. 重点是两位减法运算电路的设计,分为两种情况:当A大于等于B时,数码管显示差值;当A小于B时,不仅显示借位信息,还需显示用补码表示的差值。补码表示法在这里发挥了关键作用,使得减法运算可以通过加法来实现,提高了计算的效率。

3. 在另一种减法运算设计中,除了满足上述条件,还要求当A小于B时,数码管显示负号,同时显示用原码表示的差值,进一步展示了不同数制表示方法的应用。

实验原理部分详细介绍了半加器和全加器的工作原理,以及它们在构建加法器中的作用。全加器的真值表和电路图被详细列出,强调了电路设计中对与非门的使用以优化延迟问题。

这篇文章深入浅出地讲解了组合逻辑电路设计中的核心概念和技术,包括二进制加减法运算的实现,以及补码和原码表示法的运用,对初学者和进阶者都有较高的实用价值。

2022-08-08 上传

2012-10-11 上传

2011-07-21 上传

2009-11-08 上传

2023-11-30 上传

点击了解资源详情

点击了解资源详情

XiZi

- 粉丝: 598

- 资源: 325

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常