OLS码在抗辐射加固设计中的应用——纠正多单元翻转错误

43 浏览量

更新于2024-09-02

收藏 413KB PDF 举报

"基于OLS码的检错纠错抗辐射加固设计"

本文主要探讨了一种针对多单元翻转(MCUs)问题的存储器抗辐射加固方案,该问题由于辐射粒子对集成电路的影响而日益突出。传统的解决方案是采用错误纠正码(ECCs),尤其是能够纠正多个错误的ECCs。在本文中,作者特别提到了使用正交拉丁方(OLS)码的故障容错系统,以应对存储器中的多个错误。

OLS码是一种一步大数逻辑可译(OS-MLD)码,其优势在于可以通过简单的逻辑电路进行译码,降低了硬件复杂度。这一特性使得OLS码在对抗多单元翻转时更具优势,尤其是在现代集成电路中,随着工艺尺寸的减小,MCUs的发生概率增加,需要更高纠错能力的ECCs。

文中介绍了ECC的基本概念,如(n, k)码,其中n是码长,k是信息位的个数。常见的ECC码如汉明码虽然在硬件开销小的情况下能纠正单个错误,但对多个错误的处理能力有限。因此,随着技术的发展,汉明码已无法满足抗辐射加固的需求。

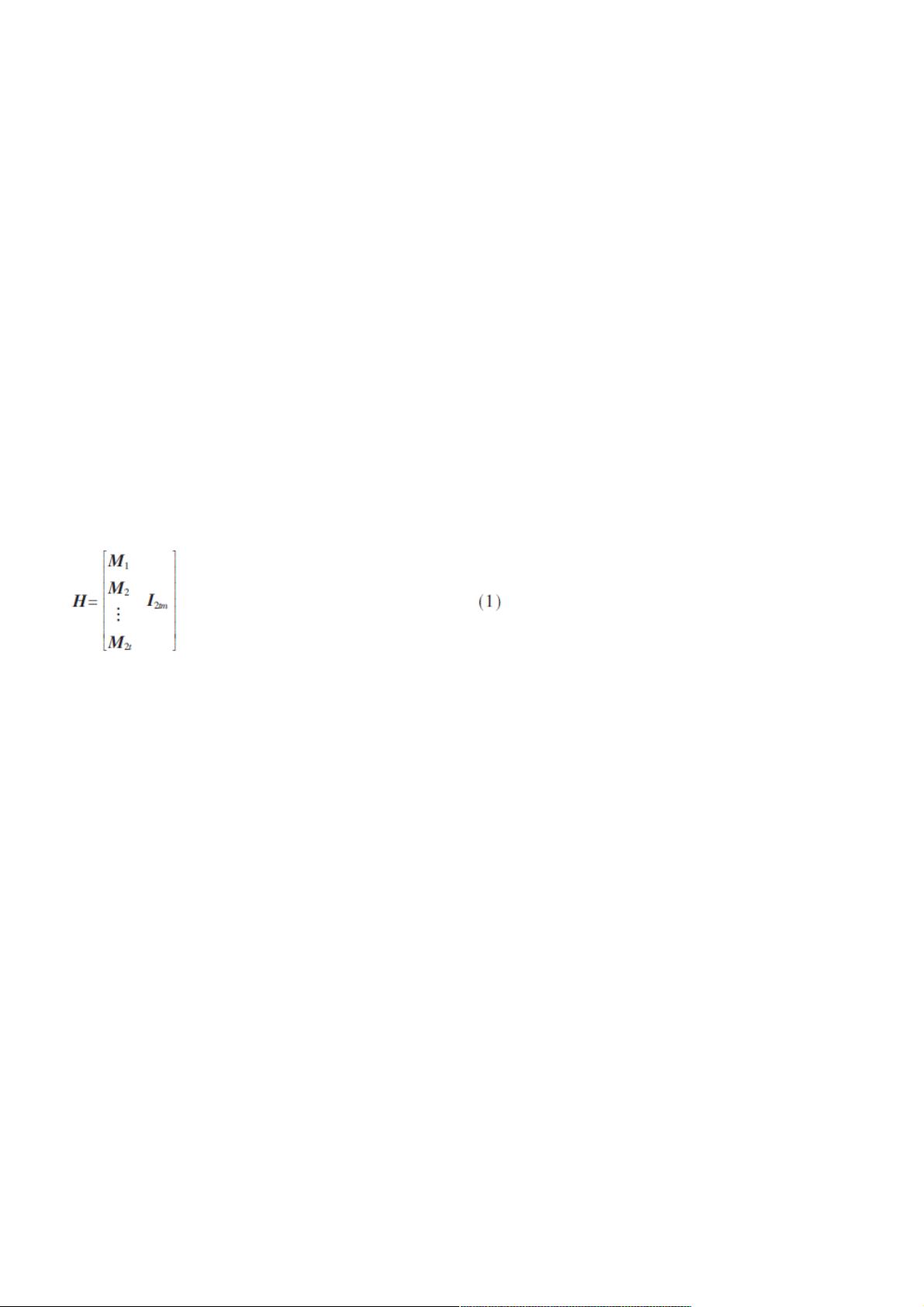

本文的设计采用了OLS码,通过构造具有特定参数(信息位k=72=49,阶数m=4,纠正能力t=2,冗余位2tm=28)的OLS码,构建了一个(77, 49)码的奇偶校验矩阵。这一设计过程涉及了正交拉丁方的理论,即两个拉丁方的正交关系,以及如何依据这一关系构造OLS码的奇偶校验矩阵。

在实现上,设计是用Verilog硬件描述语言编写的,并通过ModelSim进行功能验证,确保了设计的正确性和可行性。这样的设计为存储器提供了有效的抗辐射保护,同时减少了因增强纠错能力而带来的额外硬件负担,从而在保证可靠性的同时,兼顾了系统的效率和成本。

这篇摘要介绍了一种创新的、基于OLS码的抗辐射加固策略,该策略能够有效解决由辐射粒子引起的多单元翻转问题,提高了存储器在恶劣环境下的工作可靠性。通过使用OLS码,设计实现了高纠错能力且硬件实现相对简单的译码机制,这对于未来的高性能、低功耗、抗辐射存储系统具有重要的指导意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-27 上传

2019-09-19 上传

2021-09-26 上传

2021-05-26 上传

weixin_38745361

- 粉丝: 3

- 资源: 879

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建