X86 CPU的段式地址翻译与BIOS初始化解析

需积分: 10 73 浏览量

更新于2024-07-14

收藏 226KB PDF 举报

"本文详细介绍了X86架构CPU在段式管理下的地址形成机制,以及BIOS初始化过程中如何利用这一机制。作者陈英豪基于实验和官方手册,揭示了一些可能被误解的X86 CPU特性,并提供了相关的基础知识以帮助理解。"

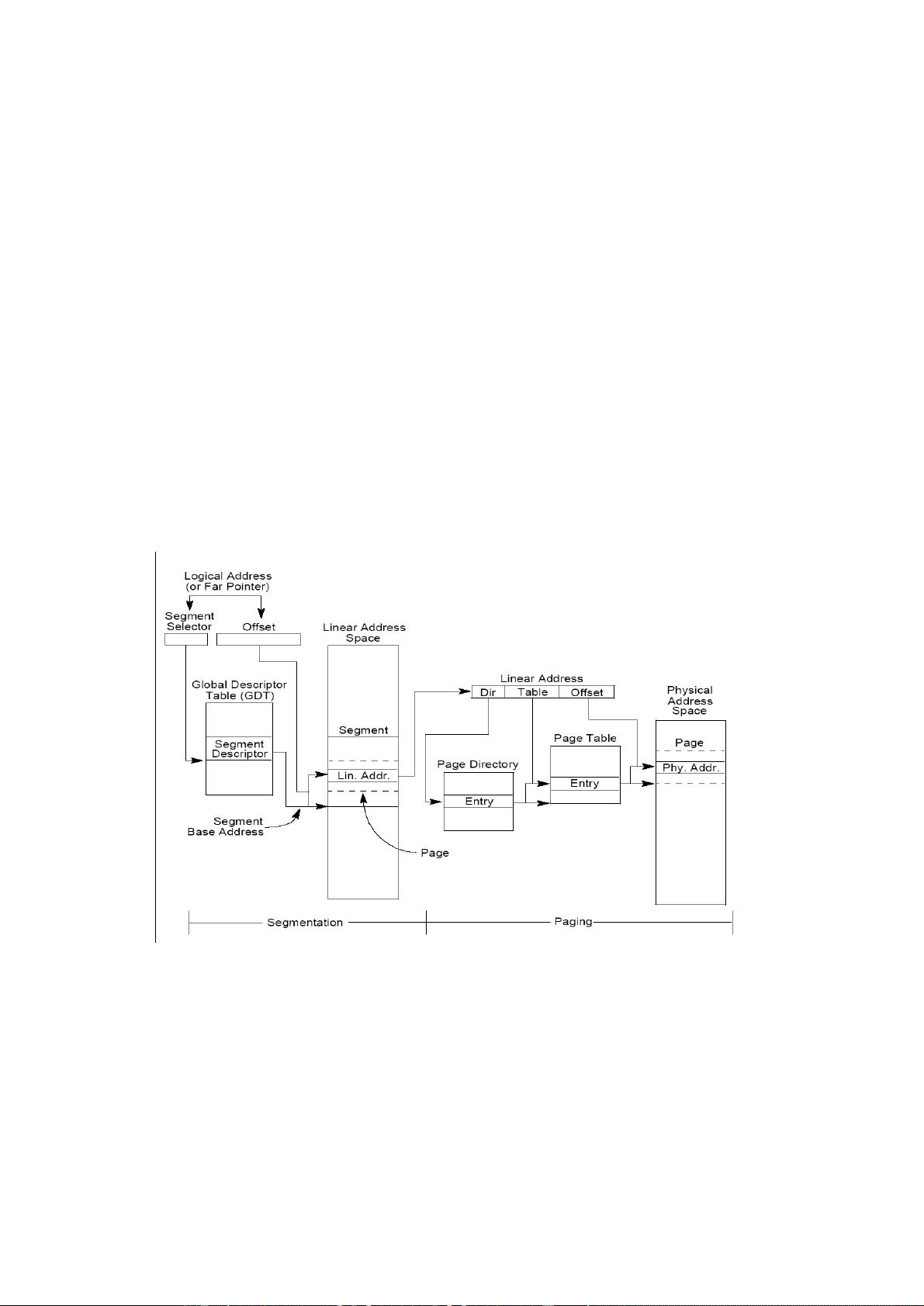

在X86架构中,CPU的地址管理采用了段式管理方式,这是出于历史原因和存储管理的需求。每个段是由一个段基址和一个偏移量组成的虚拟地址,这两者结合后通过段地址翻译机制转化为线性地址。虚拟地址是程序员在编程时使用的二维地址形式,而线性地址则是一维的,可以直接对应到物理内存地址。

段地址翻译机制的工作流程如下:首先,16位的段寄存器内容左移4位(相当于乘以16),然后加上16位的偏移量,生成20位的线性地址。如果未启用分页机制,线性地址就是直接的物理内存地址。若启用了分页,线性地址会进一步通过页地址翻译机制转换为实际的物理地址。

在实模式下,8086CPU的地址线只有20根(A0至A19),所有段寄存器和其他寄存器都是16位宽。此时的地址翻译简单直接,没有保护模式和分页的概念。但是,有一个关键点值得注意,那就是A20地址线的处理。在8086中,如果不启用A20线,CPU只能访问1MB(2^20字节)的内存,因为A20线关闭意味着最高有效位(第20位)始终为0,限制了地址空间。当需要访问超过1MB的内存时,必须开启A20线,使得20位的线性地址能完全映射到物理内存。

BIOS在初始化过程中会处理A20线的控制,确保CPU能够访问整个物理内存。这通常包括发送特定的键盘控制器命令来开启A20线,以扩展地址空间。这个过程对于现代操作系统来说是必要的,因为它们需要访问超过1MB的内存。

此外,随着CPU的发展,32位和64位的X86处理器增加了更多的地址线和更复杂的地址转换机制,如分页,以支持更大的内存空间和更高级别的内存保护。在32位模式下,线性地址扩展到了32位,而在64位模式下,线性地址可以达到64位,提供了巨大的地址空间。

总结来说,X86 CPU的地址形成机制是其内存管理的核心部分,涉及到段寄存器、偏移量、线性地址和物理地址的转换,以及在不同模式下(如实模式、保护模式)的适应性变化。理解和掌握这一机制对于深入理解X86系统的工作原理至关重要。

2021-09-24 上传

2021-09-24 上传

2022-05-03 上传

2019-05-21 上传

2021-06-30 上传

2021-09-24 上传

2022-02-28 上传

2021-12-06 上传

2021-09-24 上传

明时此至

- 粉丝: 2

- 资源: 6

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案