ASIC Implementation of a Low Power

BaseBand-Processor for UHF RFID Tag

Zhu Qiuling, Zhang Chun, Wang Xiaohui, Liu Zhongqi, Li Yongming, Wang Zhihua

Institute of Microelectronics, Tsinghua University

Beijing, 100084, P.R.China

Email: Zhuql07@mails.tsinghua.edu.cn

Abstract

——

A novel digital baseband processor of an UHF RFID

tag was presented based on the ISO/IEC 18000-6 type C

standard. In order to enhance the signal-noise ratio in the return

link, spread spectrum technique is used in addition to the FM0

encoding/Miller sub-carrier modulation. The tag supports all the

11 mandatory commands which are required by the 6C standard

as well as the implementation of probabilistic/slotted

anti-collision scheme and read/write operation to EEPROM.

Low power techniques are adopted to reduce the instantaneous

power and average power. The chip was designed and fabricated

using 0.18um 6 metal layers CMOS technology. Area of the

proposed baseband processor is 0.5mm

2

. From the measurement

result, the overall power consumption is about 16uW at the

minimum voltage of 1.04V.

Index Terms — RFID ; baseband processor; low power;

spread spectrum

EEACC: B10

CLC number: TN409 Document Code: A

0 INTRODUCTION

Nowadays the application of Radio Frequency

Identification (RFID) can be found in more and more fields,

such as logistics, manufacturing and transportation, as well as

tickets, mobile phones, secure access and many more

[1]

. To

meet the sharply increasing market requirements, the preferred

RFID system must exhibit features like low cost, long

operation range and high data rate, requiring small and low

power passive fully integrated circuits.

Tags usually work in adverse environments, so it is

important to enhance their anti-disturbance capacities and

reduce the Bit Error Rate (BER) of RFID communication.

What’s more, the mass usage of RFID has raised concerns

regarding security and privacy issues

[2]

.

In this paper, we present a high performance digital

processor of passive UHF RFID tag in fully compliance with

but not limited to the ISO/IEC 18000-6 type C standard which

takes into account of the issues mentioned above——of

low-power and low-BER, as well as the strong anti-disturbance

capacities.

This paper is organized as follows. In Sect.1 and Sect.2

below, the air interface standard and system architecture are

presented, while Sect.3 more specifically describes the low

power strategies in the design of each sub-module. Realization

of spread spectrum is presented in Sect.4. Sect.5 discusses the

ASIC implementation and verification result. Further expected

development and conclusions are eventually drawn in Sect.6

1.

AIR INTERFACE STANDARD

In 2006, the EPC Class-1 Generation-2 UHF RFID

Protocol was absorbed into the ISO/IEC18000 series of RFID

standard as ISO/IEC 18000-6 Type C, accommodating the

latest development of passive RFID technology in the UHF

frequency band in the air interface communication

[3]

.

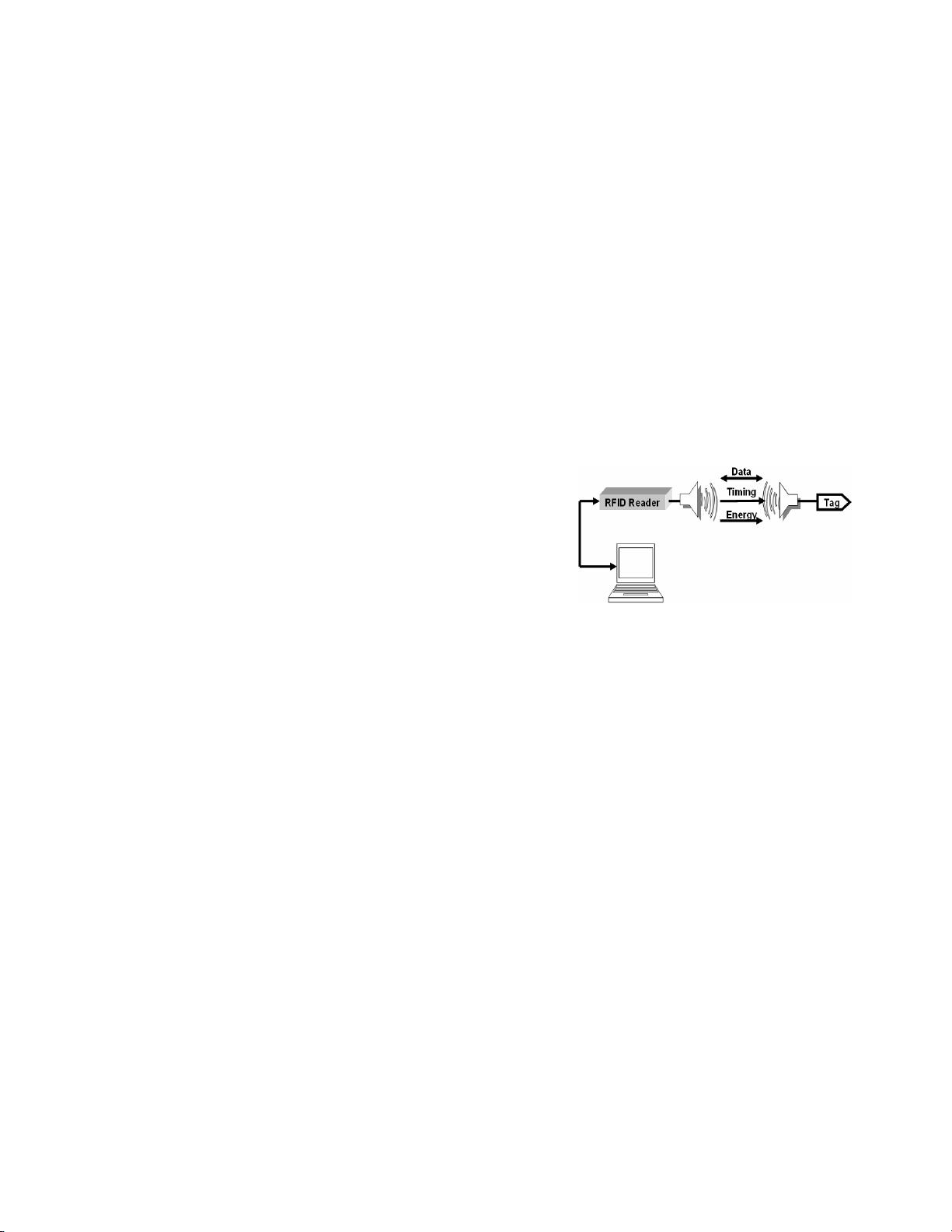

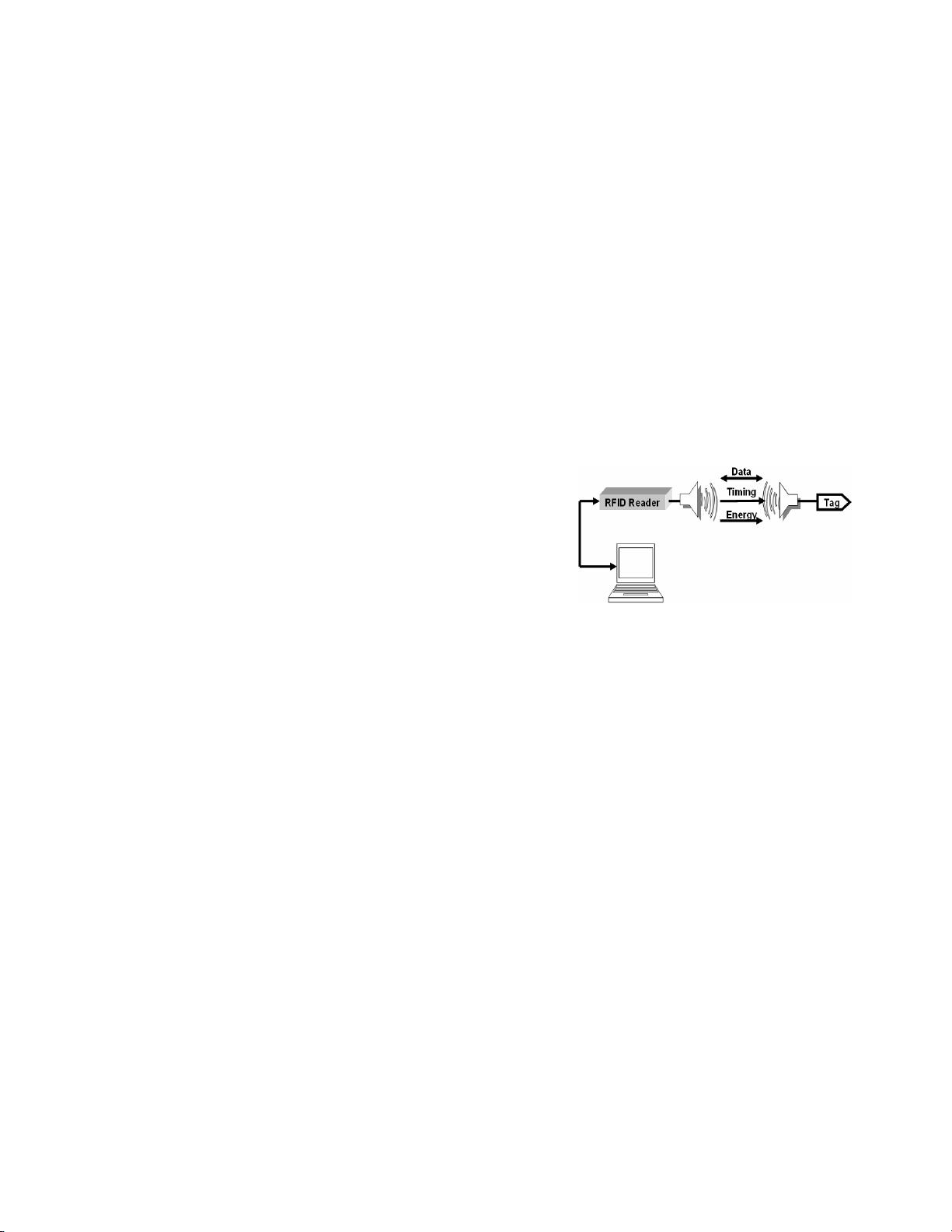

The RFID system is shown in fig.1. Interrogators transmit

information to tags by modulating RF signals in the 860 MHz

to 960 MHz frequency range, the tags receive both information

and operating energy from this RF signal. The interrogator

receives information from a tag by transmitting an

un-modulated RF signal to the tag and listening for a

backscattered reply. The tag responds by modulating the

reflection coefficient of its antenna, thereby backscattering an

information signal to the interrogator

[3]

. Tags are usually

passive, meaning that they receive all of their operating energy

from the interrogator’s RF waveform.

2.

SYSTEM ARCHITECTURE AND REQUIREMENT

Baseband-processor is one of the major parts of the RFID

tag, which determines the tag functions and performance.

The baseband-processor fully implements the ISO/IEC

18000-6 type C standard, which performs PIE decoding, CRC

checking, probabilistic/slotted anti-collision arithmetic,

memory accessing, FM0 encoding, as well as all the inventory

and assess commands such as the select, query, write, read,

lock, kill and so on.

Various techniques are taken to achieve high performance.

Major considerations focus on the power issues especially the

peak power in each sub-module design

[4]

. Moreover, Spread

Fig.1. RFID system

图1 RFID 系统