Quartus II: 74160八进制计数器与JK触发器实战教程

下载需积分: 41 | DOC格式 | 1.45MB |

更新于2024-09-02

| 151 浏览量 | 举报

本资源是一份关于使用Quartus II 软件进行电子技术EDA仿真实验的详细指南。实验主要围绕两个核心内容展开:同步八进制计数器的实现和由JK触发器实现的同步七进制加法计数器。

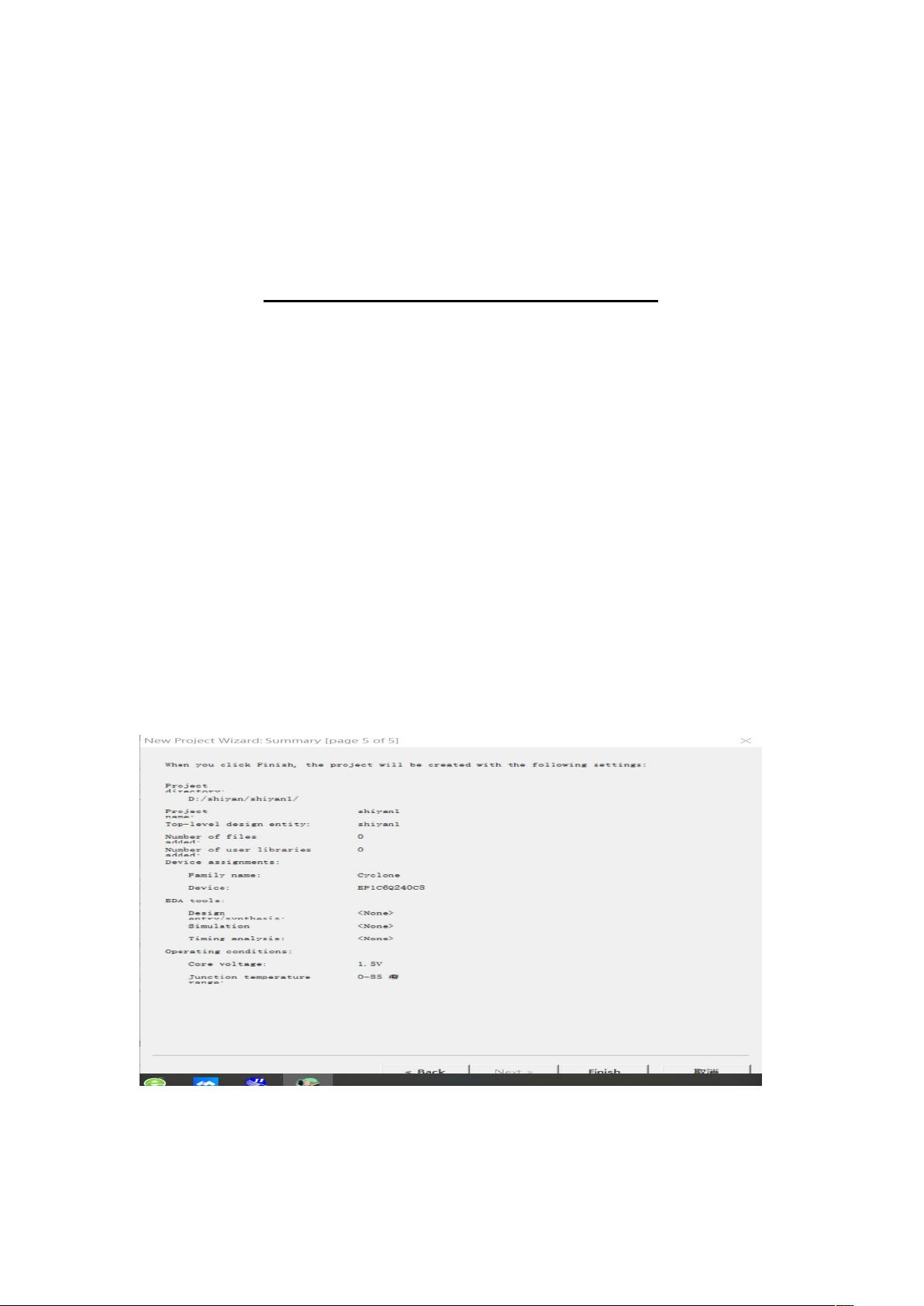

首先,实验以74160芯片为例,通过Quartus II 来设计一个同步八进制计数器。学生需要熟悉软件的工作流程,包括设计输入阶段,即在软件中设置74160的各个引脚功能,如异步清零端CLK、同步置数端LDN等,并将其与输入信号连接。设计者特别强调了低电平有效的使能端和A、B、C、D端的使用。在编译过程中,学生会学习如何将电路原理转化为硬件描述语言(HDL),如Verilog或VHDL。时序仿真环节则模拟了实际工作中的时间延迟,展示了不同输出引脚与系统时钟(cp脉冲)的关系,如QA输出的cp脉冲2分频等。

接着,实验转向由JK触发器构建的同步七进制加法计数器。在这个部分,学生需要设计电路,根据状态变化进行计数和清零操作。在功能仿真和时序仿真中,可以看到计数器的工作状态和可能遇到的竞争现象,如在时序仿真的波形图中观察到的毛刺。

整个实验过程中,学生不仅掌握了Quartus II 软件的基本使用方法,还深入了解了可编程逻辑器件(FPGA)的设计流程,包括设计输入、编译、仿真以及定时分析。通过实际操作,他们能够将理论知识与实践相结合,提升设计和调试数字逻辑电路的能力。

此外,实验报告中包含了电路图、编译报告和仿真报告的关键截图,以及实验数据分析,这些内容有助于学生巩固理论知识,同时也为他人提供了参考和学习的实例。最后,实验总结部分提炼了关键的学习心得和建议,如理解软件设计流程、处理时间延迟问题等,对于进一步提高电子设计技能具有指导意义。

相关推荐

qq_43786094

- 粉丝: 0

最新资源

- 初学者入门必备!Visual C++开发的连连看小程序

- C#实现SqlServer分页存储过程示例分析

- 西门子工业网络通信例程解读与实践

- JavaScript实现表格变色与选中效果指南

- MVP与Retrofit2.0相结合的登录示例教程

- MFC实现透明泡泡效果与文件操作教程

- 探索Delphi ERP框架的核心功能与应用案例

- 爱尔兰COVID-19案例数据分析与可视化

- 提升效率的三维石头制作插件

- 人脸C++识别系统实现:源码与测试包

- MishMash Hackathon:Python编程马拉松盛事

- JavaScript Switch语句练习指南:简洁注释详解

- C语言实现的通讯录管理系统设计教程

- ASP.net实现用户登录注册功能模块详解

- 吉时利2000数据读取与分析教程

- 钻石画软件:从设计到生产的高效解决方案