Altera Cyclone PLL 动态配置指南:解锁FPGA时钟灵活性

需积分: 24 82 浏览量

更新于2024-07-22

收藏 1.73MB DOC 举报

本文档详细阐述了Altera Cyclone系列FPGA中的PLL(锁相环)使用和配置。在实际应用中,FPGA的工作时钟需求可能会随时间变化,这要求PLL能够适应不同频率的输入。当输入时钟频率变化不大时,PLL通常能自我调整并重新锁定,确保稳定输出。然而,如果频率变化过大(例如从50MHz跳到200MHz),PLL可能无法重新锁定,导致输出时钟频率不可预知。

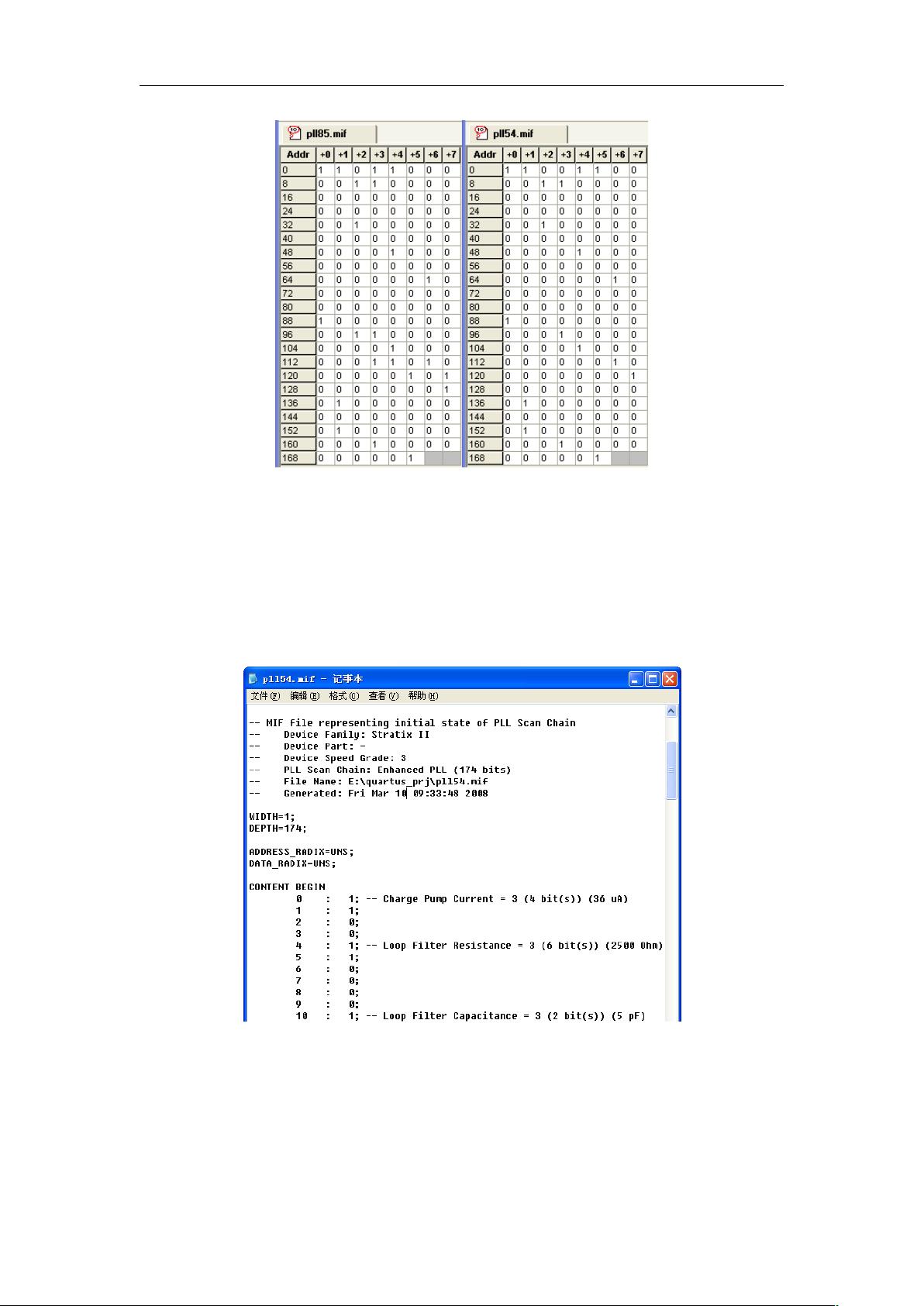

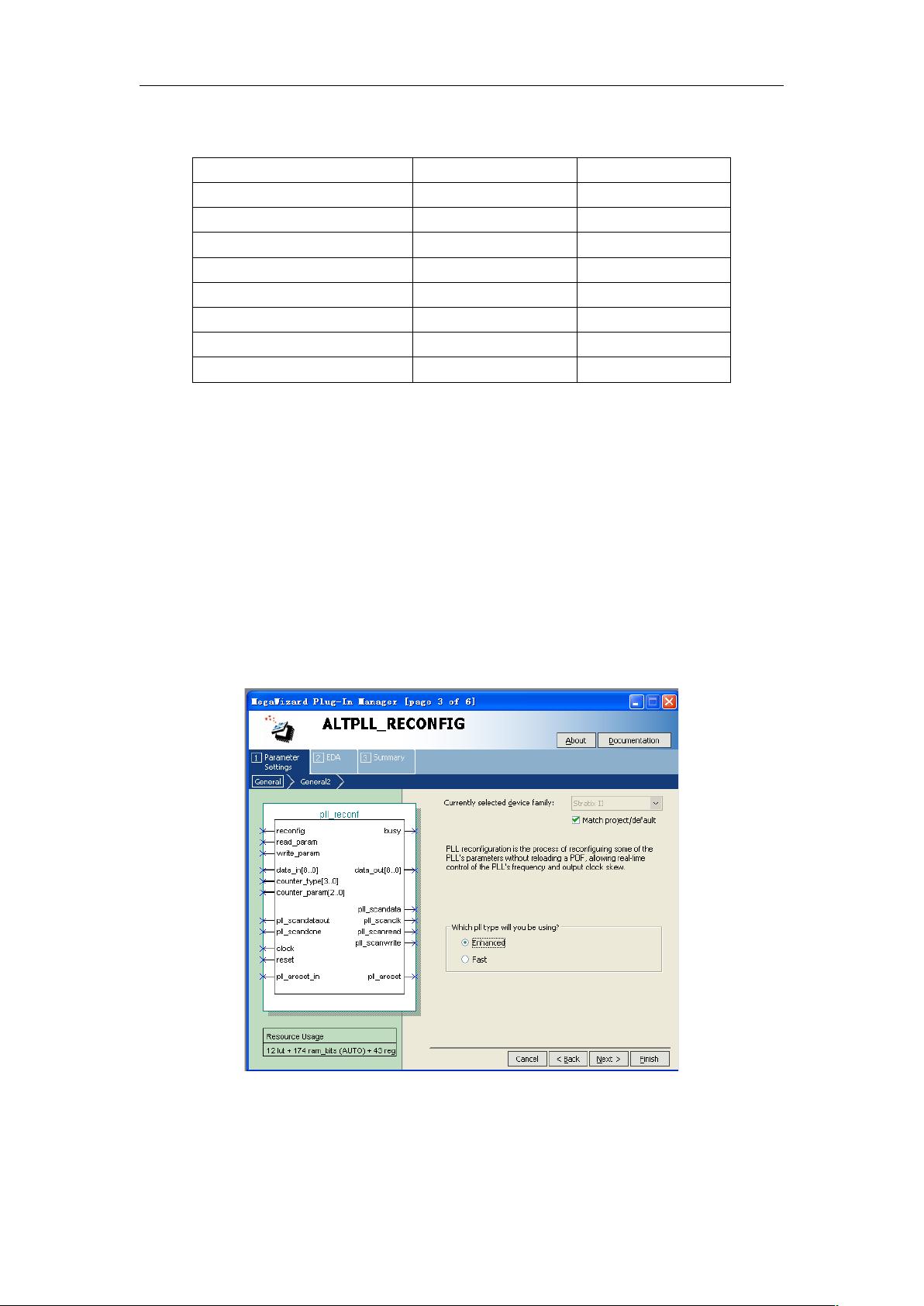

针对这种情况,提出了两种处理方法。方法一是为每个可能的输入频率配置独立的PLL,通过内部逻辑选择合适的时钟源。这种方法直观但消耗较多的PLL资源。方法二是利用FPGA制造商提供的可重新配置PLL功能,如Altera的ALTPLL_RECONFIG宏模块,允许通过软件调整PLL参数以适应新频率,尽管实现复杂但节省资源。能否实现实时重新配置取决于FPGA是否支持这种功能,建议查阅对应厂商的手册。

本文以Altera Stratix II系列FPGA为例,展示了其内嵌的增强型可重配置PLL如何在输入时钟频率变化时动态调整,旨在通过提供PLL的重新配置能力,无需硬件更改即可通过软件手段进行调整,确保 PLL 的稳定工作。PLL的基本结构包括模拟电路,如相位频率检测器(PFD)和压控振荡器(VCO)。PFD负责检测输入时钟与反馈时钟的相位差,VCO根据这个信号调整自身的频率。通过这种机制,PLL能够锁定输入时钟并保持稳定的输出频率,从而满足各种工作场景的需求。

2019-02-02 上传

2018-10-12 上传

2024-01-10 上传

2023-05-16 上传

2023-12-22 上传

2023-07-29 上传

2023-11-28 上传

2023-05-13 上传

teliduxingdeji

- 粉丝: 5

- 资源: 20

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展