MachXO2设备用户闪存和强化控制功能参考指南

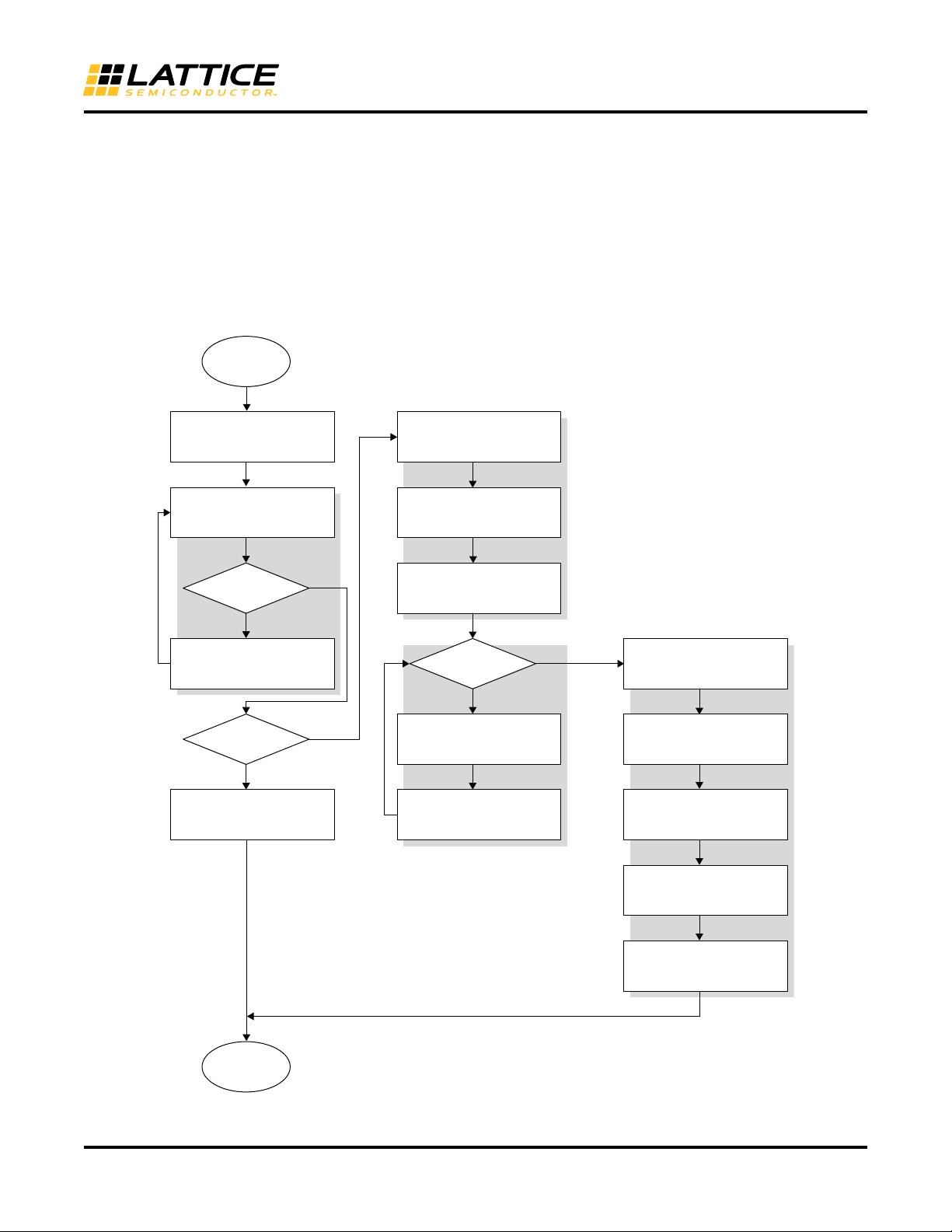

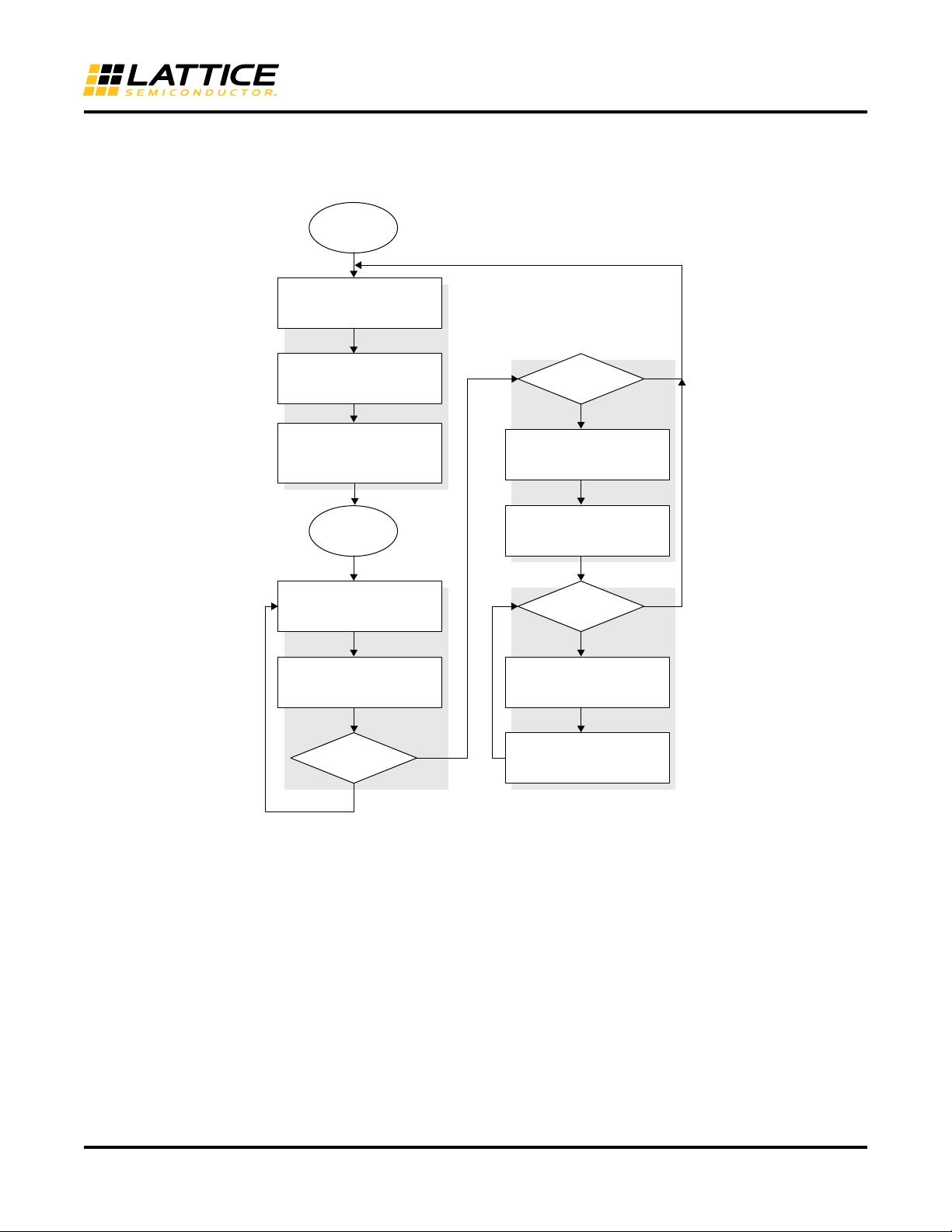

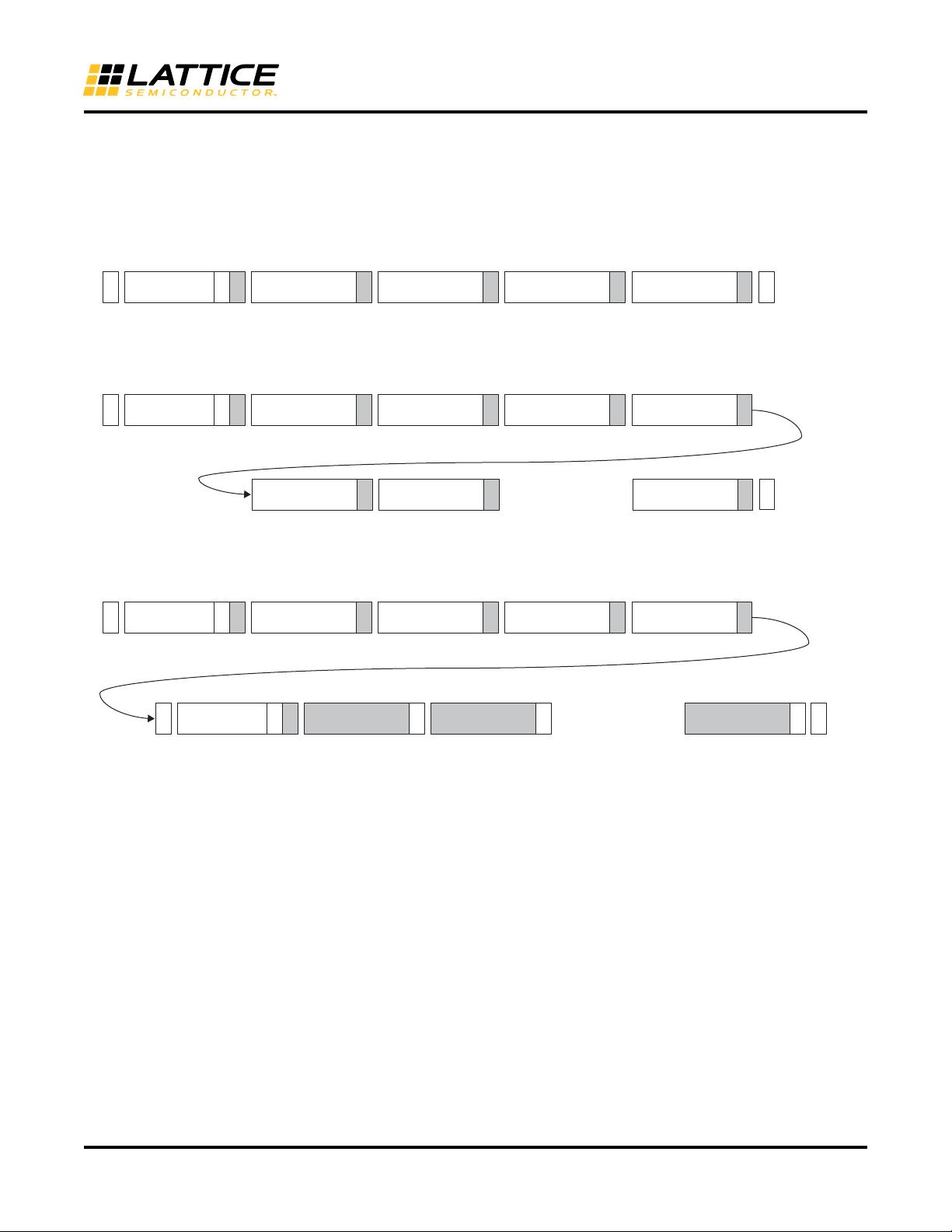

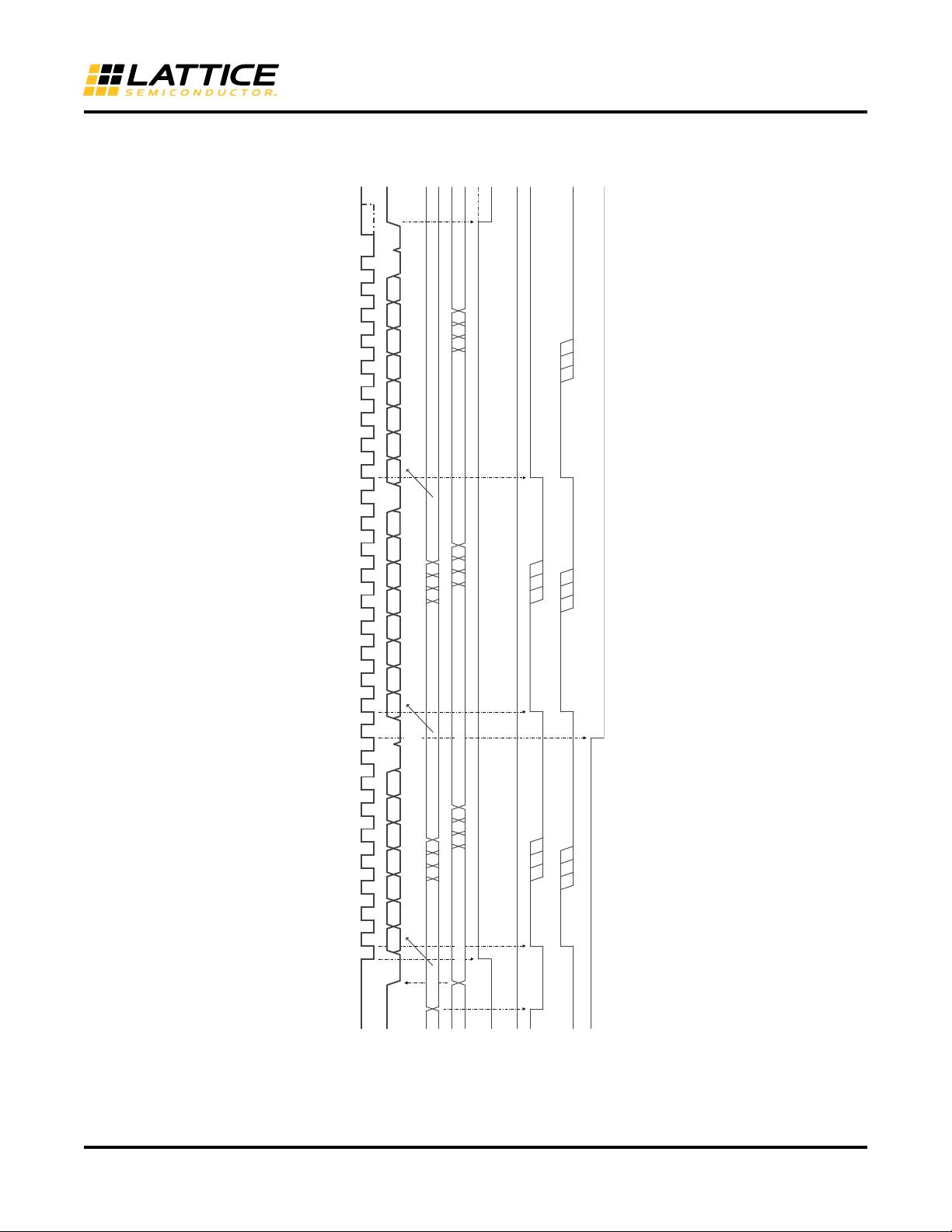

本参考指南是Lattice Semiconductor Corporation于2016年11月发布的关于MachXO2系列FPGA设备的补充文档,编号为TN1246_2.4。这份技术笔记主要针对TN1205《在MachXO2器件中使用用户闪存内存和强化控制功能》的使用指南进行扩展,着重讲解如何利用MachXO2 FPGA的独特特性,如高性能、低功耗的FPGA架构,以及内置的硬核控制功能和片上用户闪存记忆体(User Flash Memory, UFM)。 在MachXO2 FPGA中,硬核控制功能是一项关键特性,它旨在简化设计实施并节省通用资源,如查找表(LUTs)、寄存器、时钟和布线。这些硬核控制函数物理上位于嵌入式功能块(Embedded Function Block, EFB)中,所有MachXO2设备都包含一个EFB模块。通过使用EFB,设计师能够高效地实现各种控制逻辑,减少了对基础逻辑资源的需求,从而提高设计的灵活性和性能。 WISHBONE协议在这份指南中也得到了详尽的阐述,这是一种开放的系统互连标准,允许不同部件之间无缝通信,使得用户可以在MachXO2设备上构建更复杂的应用。该协议提供了低级和高级接口,支持数据传输、系统管理和错误处理等功能。 EFB Register Map部分详细列出了EFB内的寄存器及其功能,这对于理解和配置硬核控制功能至关重要。通过理解这些寄存器的作用,开发者可以精确地设置和管理控制逻辑的行为。 Command Sequences部分则展示了如何通过命令序列来操作用户闪存内存和硬核控制功能。这部分内容通常包括编程步骤、数据加载和执行控制操作的详细流程,有助于开发者编写高效的代码和调试策略。 最后,Examples部分提供了实际应用案例和示例代码,以帮助读者更好地理解和应用这些功能。这些例子可能涉及不同的领域,如数字信号处理、嵌入式系统设计或实时控制等。 总结来说,MachXO2 Devices Reference Guide提供了深入的技术细节,使设计者能够充分利用MachXO2 FPGA的硬核控制功能和用户闪存内存,实现高效能、低功耗的设计,并通过WISHBONE协议与其他系统组件协作。通过阅读和实践这份指南,设计师可以显著提升其在MachXO2平台上的开发能力。

剩余81页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 掌握数学建模:层次分析法详细案例解析

- JSP项目实战:广告分类系统v2.0完整教程

- 如何在没有蓝牙的PC上启用并使用手机蓝牙

- SpringBoot与微信小程序打造游戏助手完整教程

- 高效管理短期借款的Excel明细表模板

- 兄弟1608/1618/1619系列复印机维修手册

- 深度学习模型Sora开源,革新随机噪声处理

- 控制率算法实现案例集:LQR、H无穷与神经网络.zip

- Java开发的HTML浏览器源码发布

- Android闹钟程序源码分析与实践指南

- H3C S12500R升级指南:兼容性、空间及版本过渡注意事项

- Android仿微信导航页开门效果实现教程

- 深度研究文本相似度:BERT、SentenceBERT、SimCSE模型分析

- Java开发的zip压缩包查看程序源码解析

- H3C S12500S系列升级指南及注意事项

- 全球海陆掩膜数据解析与应用

信息提交成功

信息提交成功