Verilog HDL设计:阻塞与非阻塞赋值及移位寄存器

需积分: 9 52 浏览量

更新于2024-07-24

收藏 2.02MB PPT 举报

"Verilog HDL设计进阶"

在Verilog HDL设计中,理解并熟练运用过程结构中的赋值语句至关重要。本章节主要聚焦于阻塞式赋值(blocking assignment)和非阻塞式赋值(non-blocking assignment)的区别与应用。

阻塞式赋值(6.1.1)通过`=`符号实现,它会立即更新目标变量的值。在执行过程中,如果赋值语句在同一个进程中连续出现,后面的语句会等待前面的赋值完成。这种赋值方式适用于组合逻辑的描述。

非阻塞式赋值(6.1.2)则使用`<=`符号,它将赋值延迟到当前过程结束时进行。在同一个进程中,非阻塞式赋值的执行顺序并不重要,因为它们都会在过程的最后同时生效。非阻塞赋值是描述时序逻辑的关键,特别是寄存器和触发器的行为。

深入理解阻塞和非阻塞式赋值(6.1.3)的内在规律对于避免设计中的陷阱至关重要。阻塞赋值可能导致逻辑顺序错误,而非阻塞赋值则可能引发数据竞争。正确使用这两种赋值方式可以确保设计意图准确无误地转化为硬件行为。

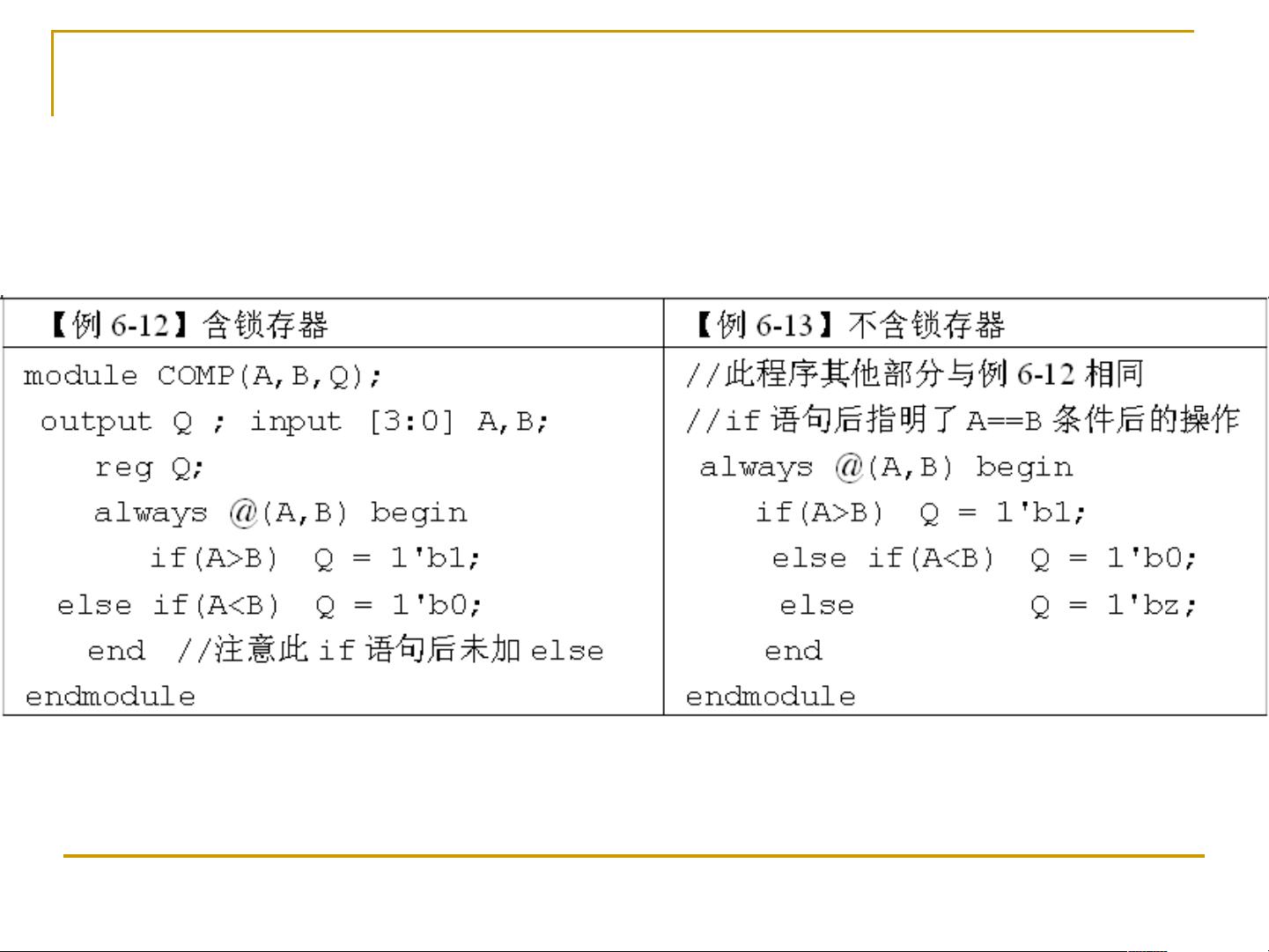

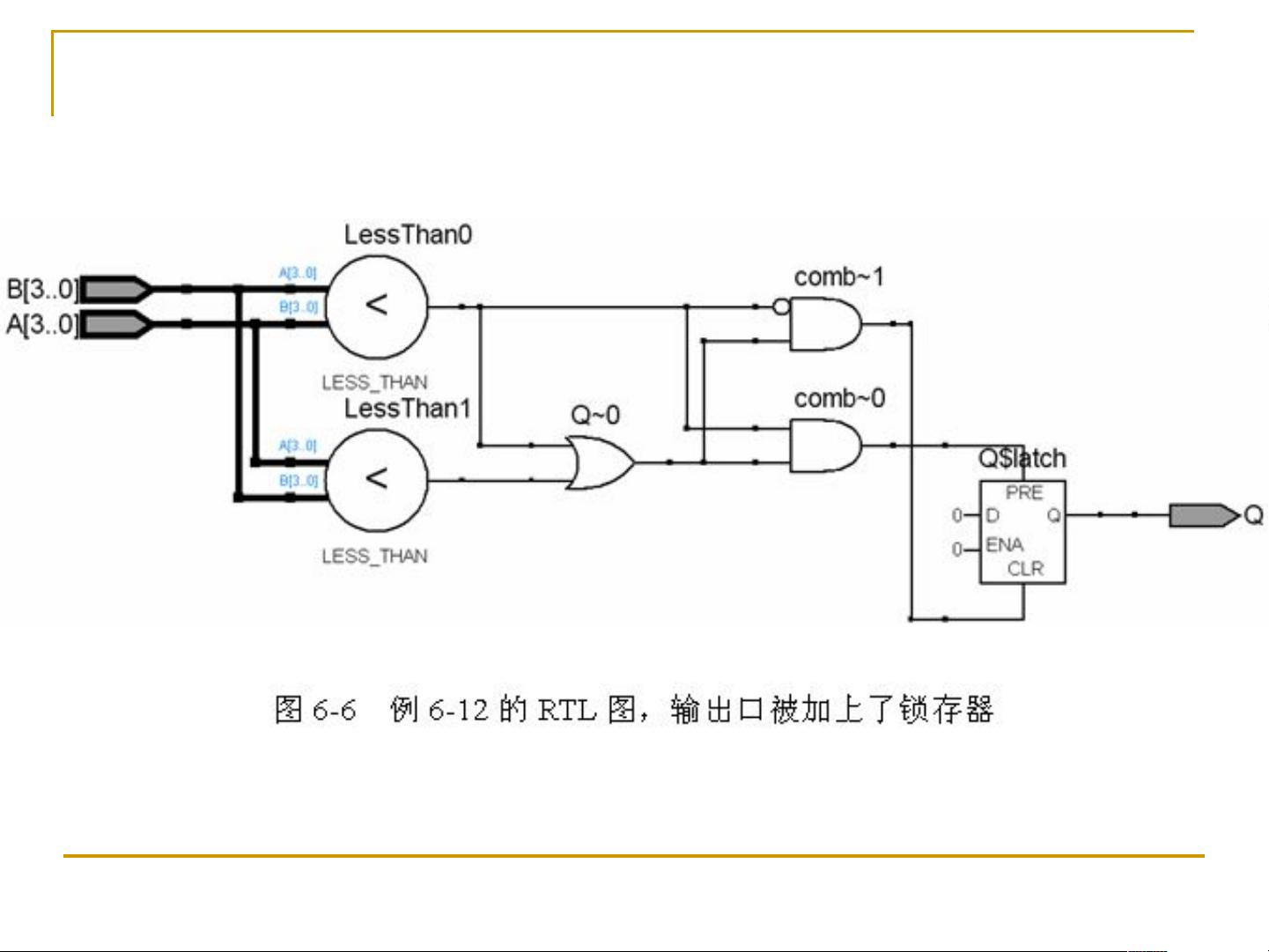

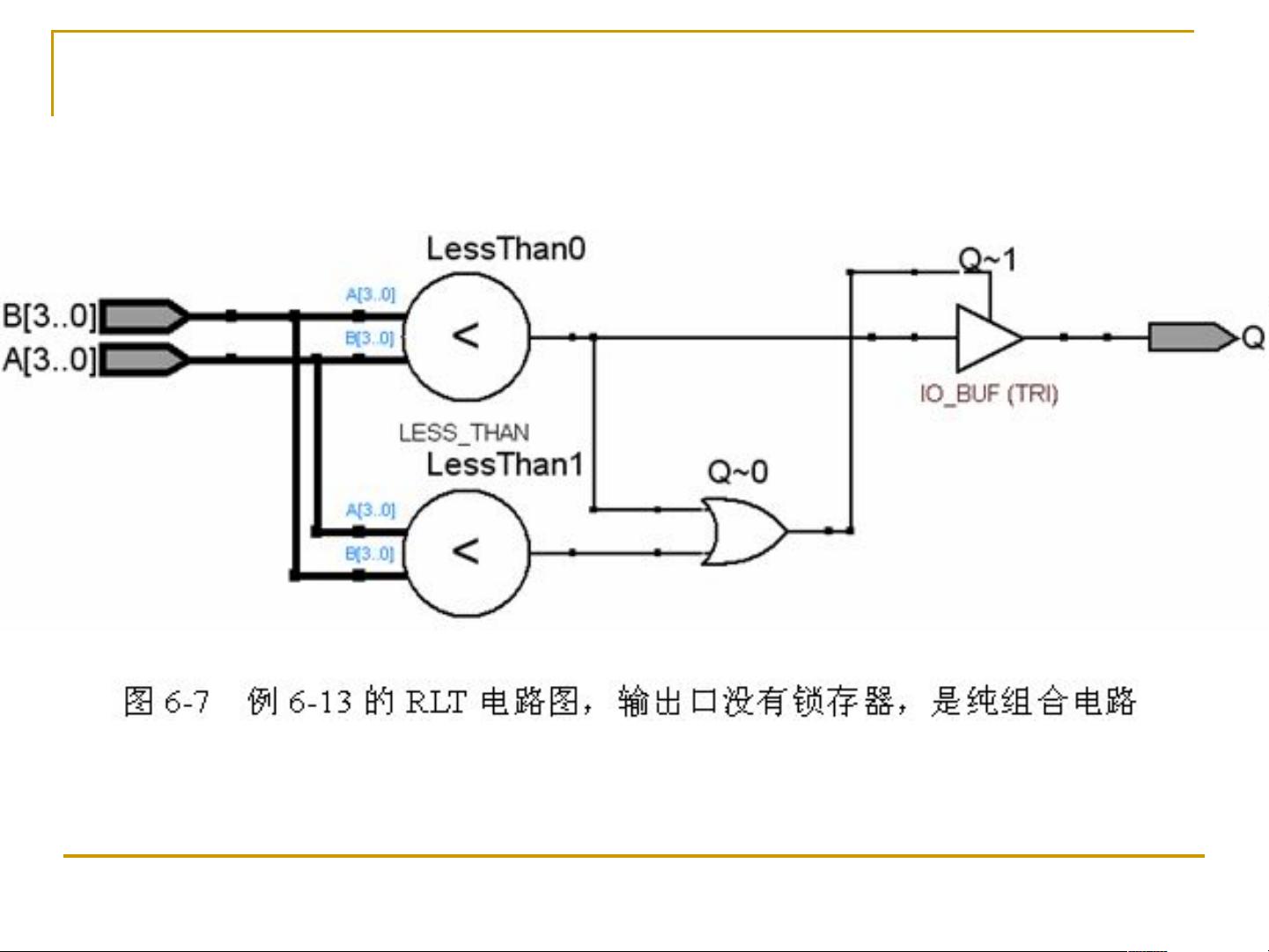

6.2章节中,讨论了过程语句(always语句)的特点和用法。always语句通常用于描述时序逻辑,它是一个无限循环语句,内部包含了事件驱动的逻辑。在这些过程中,顺序语句如if-else、for、while等既体现了程序的顺序执行特性,也展示了硬件并行执行的特性。进程语句本身是并行执行的,但其中的逻辑控制可以模拟串行行为。设计时,应确保每个always块只对应一个时钟边沿,以避免时序混乱。此外,不完整的条件语句可能影响时序电路的正确触发。

在6.3章节,探讨了移位寄存器的设计。移位寄存器是数字系统中的基本组件,用于存储和移动数据。例如,8位移位寄存器(6.3.1)可以包含同步并行预置功能,通过非阻塞赋值实现数据的左移或右移。在设计时,还可以使用特定的属性注解(如`(*synthesis, probe_port*)`)来指导综合工具和仿真器处理寄存器。6.3.2部分讲述了如何设计移位模式可控的移位寄存器,这涉及到了更复杂的控制逻辑。6.3.3节介绍如何利用移位操作符直接完成移位寄存器的设计,简化代码并提高可读性。

对比和分析不同赋值方式的结果(6.3.3)是提高设计能力的重要环节。例如,通过比较阻塞和非阻塞赋值在相同场景下的行为差异,可以加深对两种赋值的理解。此外,6.3.4节提到了使用循环语句设计乘法器,这种方法可以有效地利用循环结构来实现复杂的计算功能,而参数定义(parametrization)则允许自定义设计的参数,增加设计的灵活性和重用性。

本资源深入讲解了Verilog HDL在高级设计中的应用,包括赋值语句的使用、过程语句的控制以及移位寄存器等重要概念,旨在帮助读者提升数字系统设计的技能。

126 浏览量

839 浏览量

184 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-07-27 上传

122 浏览量

122 浏览量

GT86095296

- 粉丝: 2

最新资源

- C#打造高效会员管理系统桌面应用

- 55个UCI数据集:机器学习训练资源汇总

- Android可视化编辑器:下载指南与功能介绍

- FDS中三大Web应用文件的WAR压缩包解析

- 打造交互式商场地图的完美JS解决方案

- MATLAB求解大型稀疏网络最大群算法研究

- yzuta:CSS技术核心解读

- wbfs格式向ios转换教程与工具

- SmartDraw绿色版:快速绘制E-R图的解决方案

- 手势解锁技术在网站制作中的应用与源代码分享

- PB 9.0 运行依赖的DLL库文件列表详解

- 批量解除U盘隐藏文件的简易方法

- Matlab与NvidiaCUDA双线性插值性能比较研究

- Android平台二维码扫描技术实现与应用

- Android平台Canvas绘制机器人的技术解析

- Java环境下通过Tomcat使用DB2数据库驱动配置指南