FPGA高精度复位系统设计详解

需积分: 10 72 浏览量

更新于2024-07-17

收藏 1.77MB PPTX 举报

"本文主要探讨了FPGA中的高精度复位系统设计,包括同步复位与异步复位的比较,带PLL的复位设计,以及复位约束的设置和优化。作者彭晓恩详细讲解了相关理论和实践,旨在帮助读者理解复位系统的复杂性和重要性。"

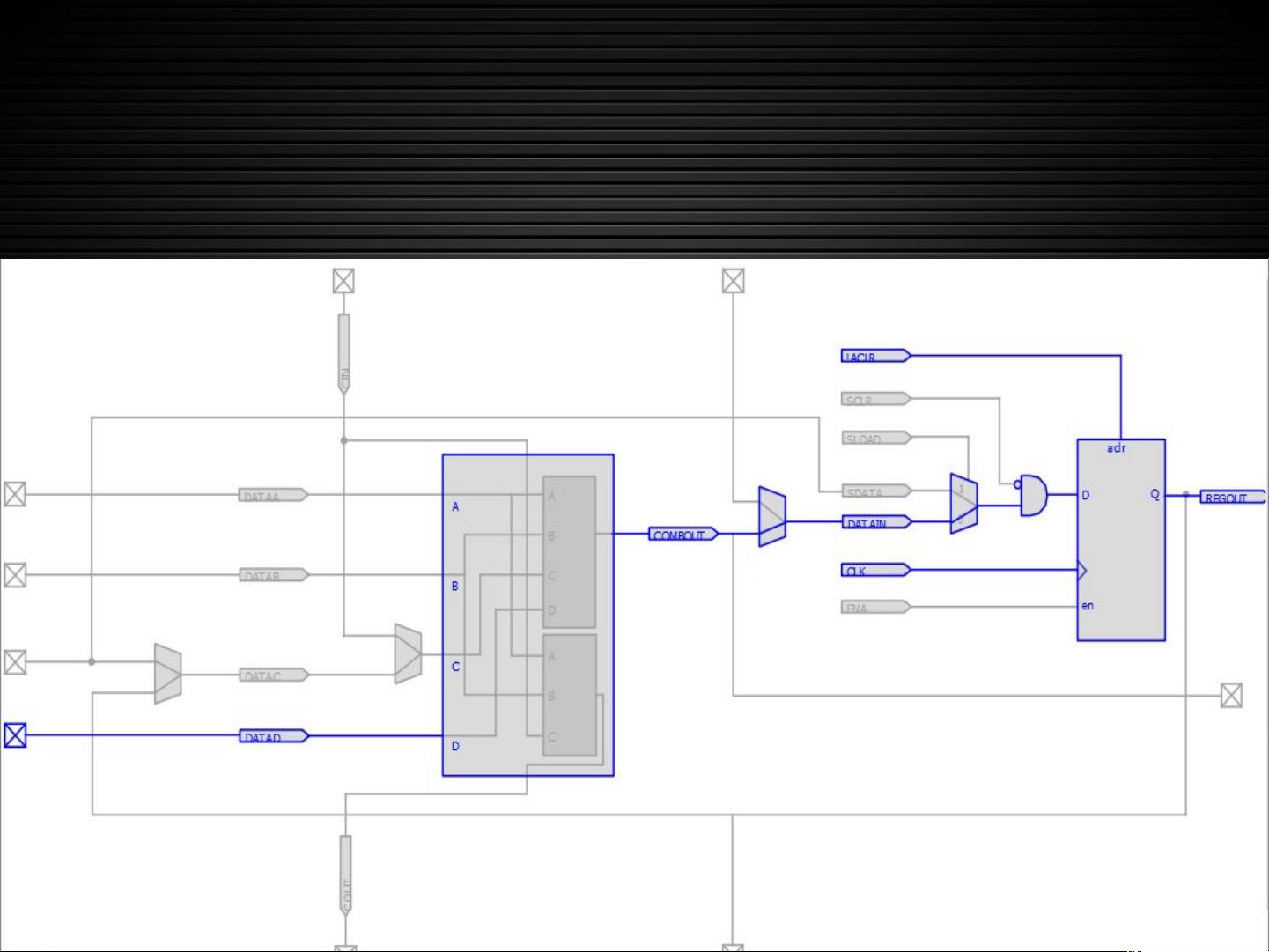

在设计FPGA的高精度复位系统时,同步复位和异步复位是两种常见的方法。同步复位的优点在于它可以过滤毛刺,减少亚稳态的出现,有利于时序分析,但其缺点是会增加硬件资源的使用并延长数据路径传输时间。相比之下,异步复位则能节省器件,提高系统响应频率,立即生效,但可能会导致亚稳态问题,尤其是在reset信号释放时。

异步复位的同步释放是一种优化方案,它结合了异步复位的即时性和同步复位的稳定性。这种方式可以避免在多时钟域中出现亚稳态,但设计时需要注意正确处理优先级。在某些应用领域,如实时系统或高精度计数器,这种设计是必要的,但也可能产生亚稳态,需要谨慎处理。

当复位系统涉及PLL(锁相环)时,设计更为复杂。PLL可以提供稳定的时钟,但其复位同步释放可能引入抖动,需要特殊考虑。ALTPLL IP Core是Altera FPGA中用于实现PLL功能的IP,其用户指南提供了关于复位端口连接和抖动管理的指导。设计中应关注复位树的完整性和抖动的影响,通过适当的设计和补偿措施来减轻这些缺陷。

在复位约束方面,Verilog HDL语言的使用者需要了解如何设置约束以优化综合结果。例如,使用`set_false_path`命令可以避免将reset信号视为关键路径,从而影响时序分析。复位优化应确保恢复时间和移除时间(Recovery Slack和Removal Slack)得到适当的计算和调整,以满足系统的时序要求。

设计FPGA的高精度复位系统需要综合考虑同步与异步复位的优缺点,合理利用PLL以提升性能,同时还要充分理解和应用复位约束,以确保系统的稳定性和可靠性。这一过程需要对数字电路、HDL编程和FPGA综合工具有深入的理解。

2021-07-13 上传

2021-07-13 上传

2020-10-19 上传

2021-07-13 上传

2010-05-15 上传

2023-03-10 上传

清霜一梦

- 粉丝: 62

- 资源: 8

最新资源

- HPUX 11i V3系统管理员指南

- DIV+CSS布局大全

- J2EE 设计开发编程

- Serial ATA 2.6 Specification

- ITIL-white

- 《LINUX与UNIX SHELL编程指南》读书笔记

- 单源最短路径问题的Dijkstra算法

- Oracle 10g R2 Concepts双语版

- 02 第四章 使用SQL语句.pdf

- spring2.5 reference

- API函数大全(32 Bit Section PowerBuilder API)

- 51汇编指令表,一目了然,希望大家多多交流学习

- Serial ATA Specification Rev. 2.5

- 01 第一~三章.pdf

- asp.net速成教程

- Understanding JTA