于敦山老师讲解:Verilog数字集成电路设计教程

需积分: 46 102 浏览量

更新于2024-07-25

收藏 2.01MB PDF 举报

"这是一份由于敦山老师提供的Verilog超详细教程,涵盖了从数字集成电路设计入门到高级应用的各个方面,旨在帮助学习者理解和掌握Verilog HDL的使用。教程内容包括Verilog的基础知识、仿真、逻辑综合以及布局布线等关键环节,还涉及到 Cadence Verilog 仿真的具体操作和实验实践。"

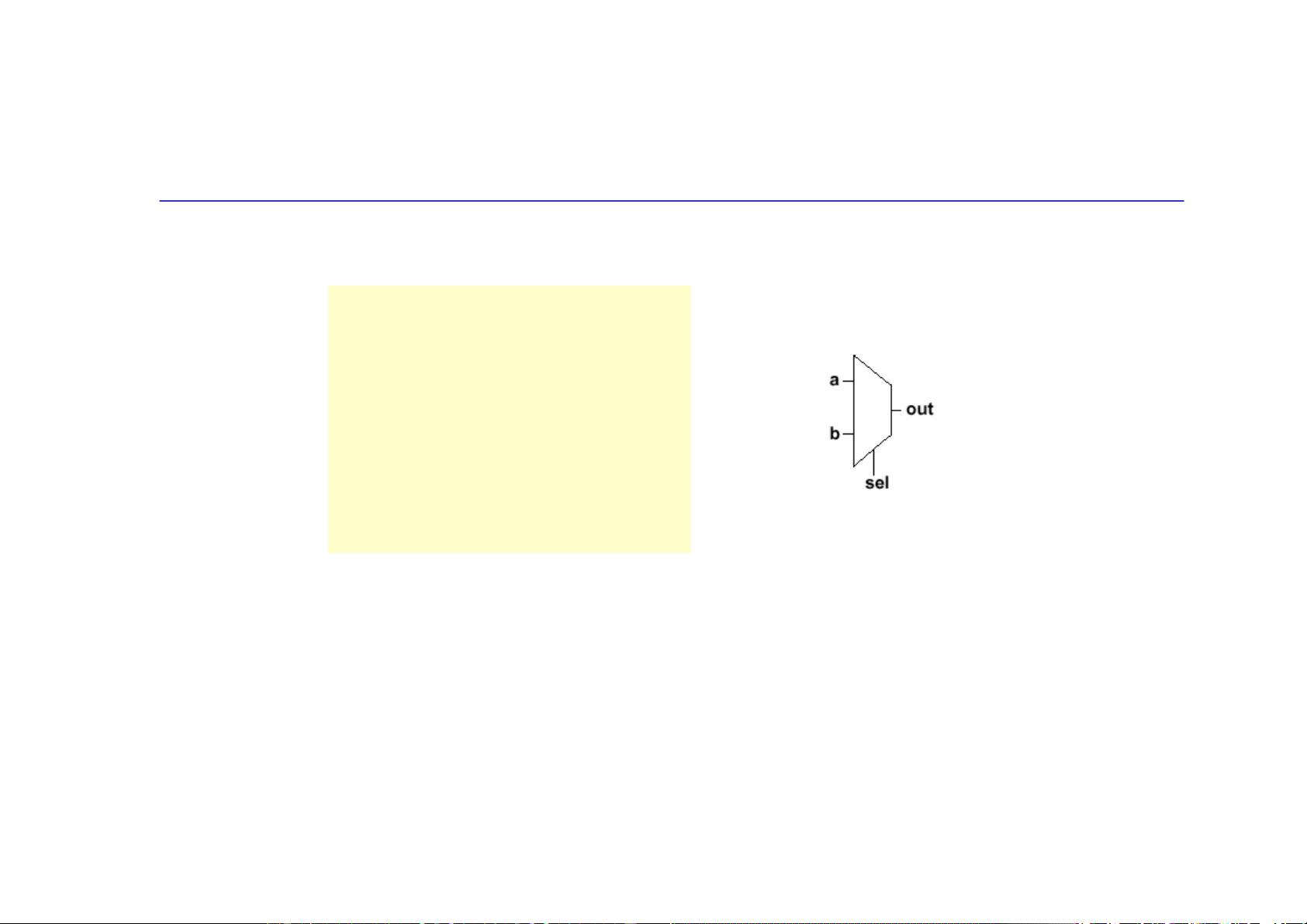

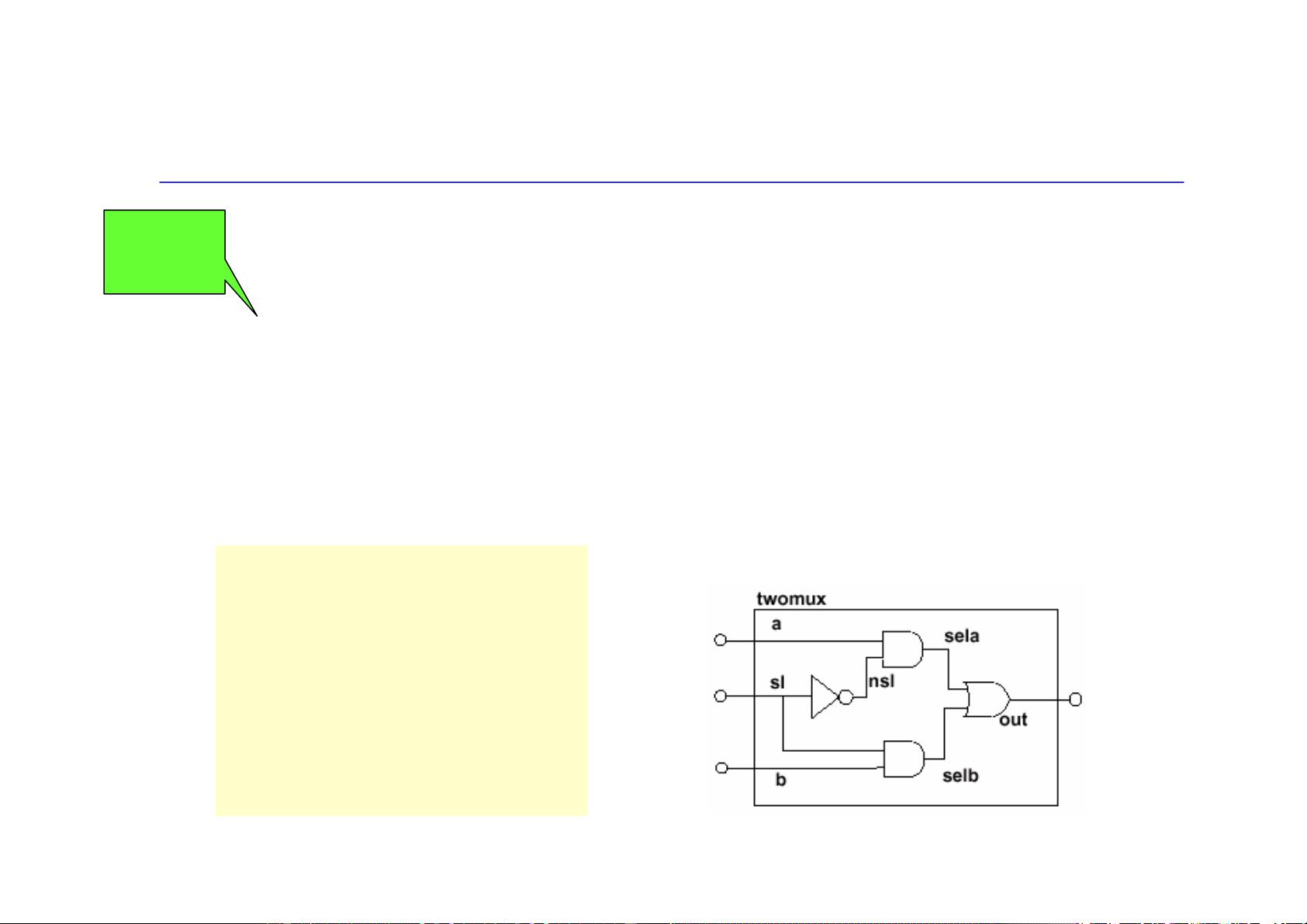

本教程首先介绍了Verilog HDL的基础,包括其在数字集成电路设计中的应用,以及语言的构成元素。Verilog的应用广泛,可用于结构级和行为级的描述,支持模拟电路的行为。结构级描述关注电路的物理结构,而行为级描述则关注电路的功能表现。课程详细讲解了如何进行结构级和行为级的仿真,同时讨论了延时的特点和testbench的创建,这对于验证设计的正确性至关重要。

在Verilog的仿真部分,教程涵盖了使用Cadence Verilog仿真器的技巧,如设计编译、源库的使用,以及不同方式的调试,包括命令行界面和图形用户界面。此外,还涉及了延时计算、性能仿真描述以及如何有效利用NCVerilog进行编译和仿真。

逻辑综合是Verilog设计流程中的重要环节,教程介绍了逻辑综合的基本概念、设计对象和静态时序分析(STA)。学习者将了解如何编写可综合的Verilog代码,并接触到Designware库和综合划分的概念,这些都是实现高效综合的关键。

设计约束的设置是确保设计满足特定性能要求的重要步骤,教程详细讲述了如何设置设计环境和约束。设计优化包括编译和有限状态机(FSM)的优化,以及如何分析和解读优化后的报告。

最后,教程还涉及到了自动布局布线工具Silicon Ensemble,这是将综合后的逻辑转化为物理芯片布局的重要工具。课程通过实验形式让学习者亲手实践Verilog设计、综合和布局布线,以加深理解。

本教程的参考书目包括了多本权威著作,如Cadence Verilog Language and Simulation等,为深入学习提供了丰富的参考资料。

这个Verilog教程是一套系统性的学习资料,适合对数字集成电路设计感兴趣的初学者和进阶者,通过理论学习与实际操作相结合,帮助学习者全面掌握Verilog HDL的设计和应用。

点击了解资源详情

点击了解资源详情

点击了解资源详情

105 浏览量

292 浏览量

2023-11-27 上传

128 浏览量

138 浏览量

171 浏览量

zhoujian198909

- 粉丝: 0

- 资源: 15

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建