基于FPGA的数字存储示波器设计与实现

版权申诉

93 浏览量

更新于2024-08-04

收藏 986KB DOC 举报

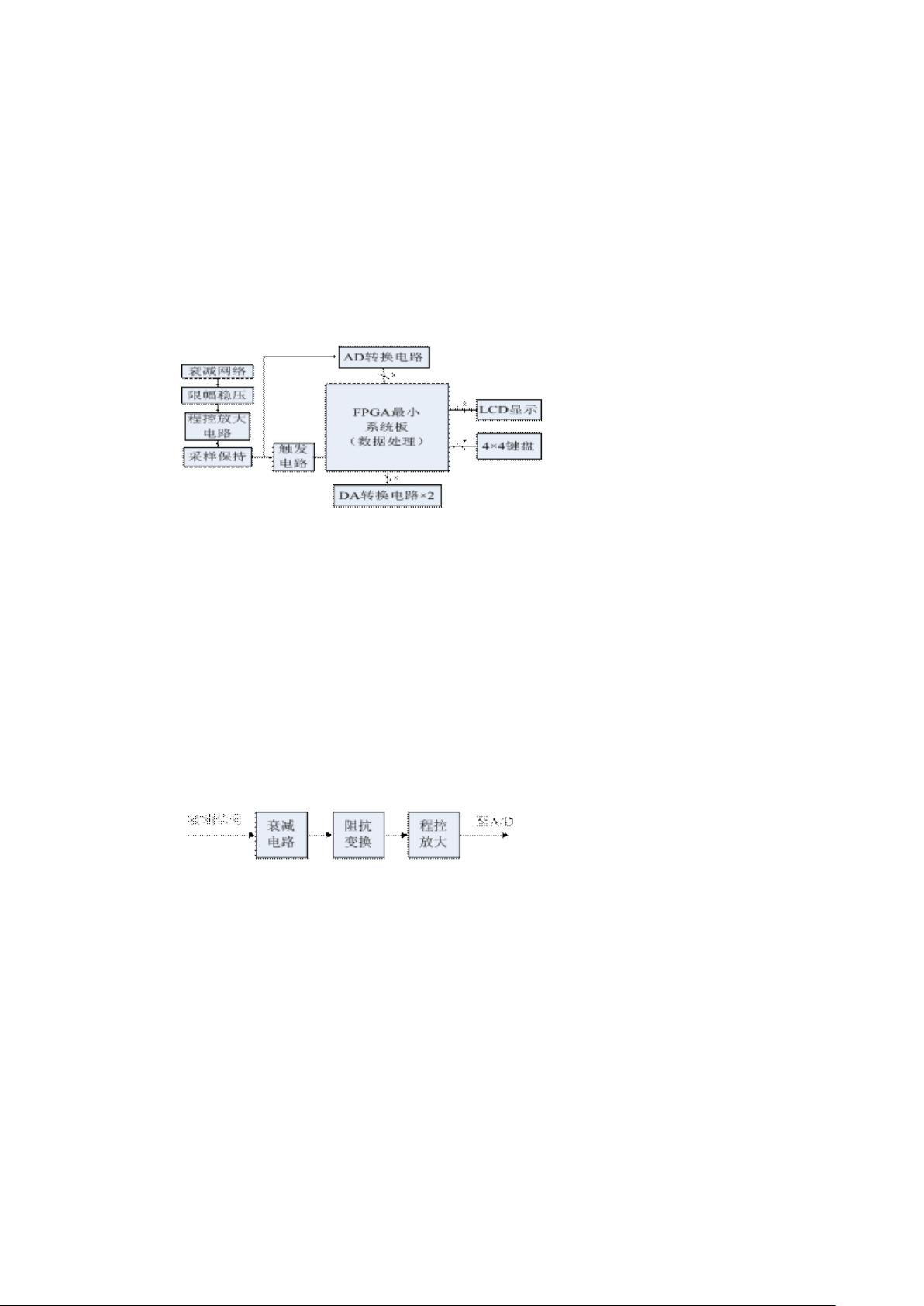

"2007年C题涉及的是数字存储示波器的设计,该设计以Xilinx公司的20万门FPGA芯片为中心,配合外围电路,包括信号调理、采样保持、内部触发、A/D转换、D/A转换和I/O模块,通过VHDL语言编程实现示波器的功能。设计涵盖了任意波形的单次触发、连续触发和存储回放,具备垂直灵敏度和扫描速度的挡位设定。系统能够对中、低频信号进行实时采样,对高频信号进行等效采样和数据存储回放,整体性能符合设计要求。主要探讨了两种设计方案,一种基于80C51单片机,另一种则利用FPGA作为核心,最终选择了FPGA方案,因为它可以快速开发,且能支持高速数据处理和存储。"

在设计数字存储示波器的过程中,首先需要理解示波器的基本工作原理。示波器是电子测量仪器,用于观察电信号的变化,它能够显示信号的幅度、频率和形状。在这个2007年的C题中,设计者面临着如何使用现代技术实现一个功能齐全的示波器的问题。

方案一采用传统的80C51单片机作为控制核心。信号首先通过调理电路调整到适合A/D转换的范围,然后由外部触发电路生成触发信号,A/D转换器将模拟信号数字化,存储在外部RAM中,最后由单片机控制D/A转换器输出。然而,这种方法在处理高采样率数据时存在局限性,因为单片机的处理速度和外接RAM的存储速度可能无法满足实时高频率数据的处理需求。

方案二选择了FPGA(Field Programmable Gate Array)作为核心,这是一种可编程逻辑器件,可以灵活地配置成各种复杂的逻辑电路。FPGA具有内置的高速存储器,可以实现双端口RAM,用于存储采样数据。此方案的优点在于,FPGA的并行处理能力能够处理高速数据流,同时,其内部资源可以快速配置,减少了开发时间和复杂性。采样保持电路确保了在采样过程中信号的稳定,而内部触发机制允许示波器对特定事件作出响应。此外,A/D和D/A转换器分别用于数字化和还原信号,I/O模块则负责与其他设备的通信。

在实现设计指标时,FPGA可以灵活控制采样频率,设置垂直灵敏度(即电压分辨率)和扫描速度(时间分辨率),以适应不同类型的信号观测。测试结果显示,该系统在中、低频信号的实时采样以及高频信号的等效采样和存储回放方面表现出色,所有指标均达到了预期。

这个设计项目展示了FPGA在高级电子系统设计中的应用,特别是对于需要高速处理和存储的应用,FPGA提供了高效且灵活的解决方案。此外,VHDL语言的使用也是现代数字系统设计的重要工具,它允许工程师以硬件描述语言的方式描述系统的逻辑行为,方便了硬件的编程和验证。

点击了解资源详情

139 浏览量

点击了解资源详情

2022-08-04 上传

143 浏览量

157 浏览量

289 浏览量

397 浏览量

102 浏览量

珞瑜·

- 粉丝: 13w+

- 资源: 500

最新资源

- talks:我讲过的各种演讲的幻灯片和资料

- ColorRampGenerator:色带生成器

- 具有dnssec支持的重要隐私,快速递归的dns解析器服务器-Golang开发

- ASP人才网内容管理系统(源代码+论文).zip

- 梅吉特

- Google浏览器安装包

- favicon-badge:一个Polymer元素,用于使用动态设置的数字声明式更新Webapp的favicon。

- react-way-immutable-flux:使用ES6,Immutable.js和Flux的React.js方法

- Trubble

- testina

- uskzvqgn.zip_相位跟踪

- my-plugin-manager:用于WordPress主题或插件的嵌入式脚本,为您的用户提供一个界面,以管理您建议与产品一起使用的插件

- 用数组实现一个线性表.zip

- Gx00_83-05-33-SNMP.zip

- imersaodev-conversoranosluz:每天从法拉利岛(Códigofeitotambémna1ª)出发。 Us programa em que quee convert anos luz emquilômetrose assim poder saber adistânciade planetas e astros

- [Android实例] Android 竖着的SeekBar.rar