ASIC低功耗设计策略与实例分析

需积分: 27 191 浏览量

更新于2024-07-17

3

收藏 2.81MB PDF 举报

本文档深入探讨了ASIC(Application-Specific Integrated Circuit)低功耗设计的方法论及实现脚本实例。首先,文章强调了低功耗设计的目的,它在现代集成电路设计中的重要性,尤其是在移动设备、物联网等需要长时间运行且电池续航能力至关重要的应用中。

低功耗设计的构成主要包括以下几个方面:

1. 功耗的构成:功耗可以根据结构进行划分,以SoC(System-on-a-Chip)为例,主要包括时钟树功耗、处理器功耗、存储器功耗、其他逻辑和IP核功耗以及输入输出pad功耗。其中,时钟树、处理器和存储器的功耗占比最高,因为它们是系统的主要活动部件。

2. 动态功耗:动态功耗主要由开关功耗和短路功耗组成。开关功耗发生在输入信号翻转时,电源对负载电容的充放电过程,计算公式涉及供电电压、负载电容和翻转速率。短路功耗则产生于输入信号翻转过程中PMOS和NMOS同时导通导致的电源直通电流。

3. 静态功耗:静态功耗主要来自CMOS电路中的漏电流,即使在没有外部信号驱动的情况下,也会有电流从电源流向漏极,这部分损耗与温度、电源电压和电路设计密切相关。

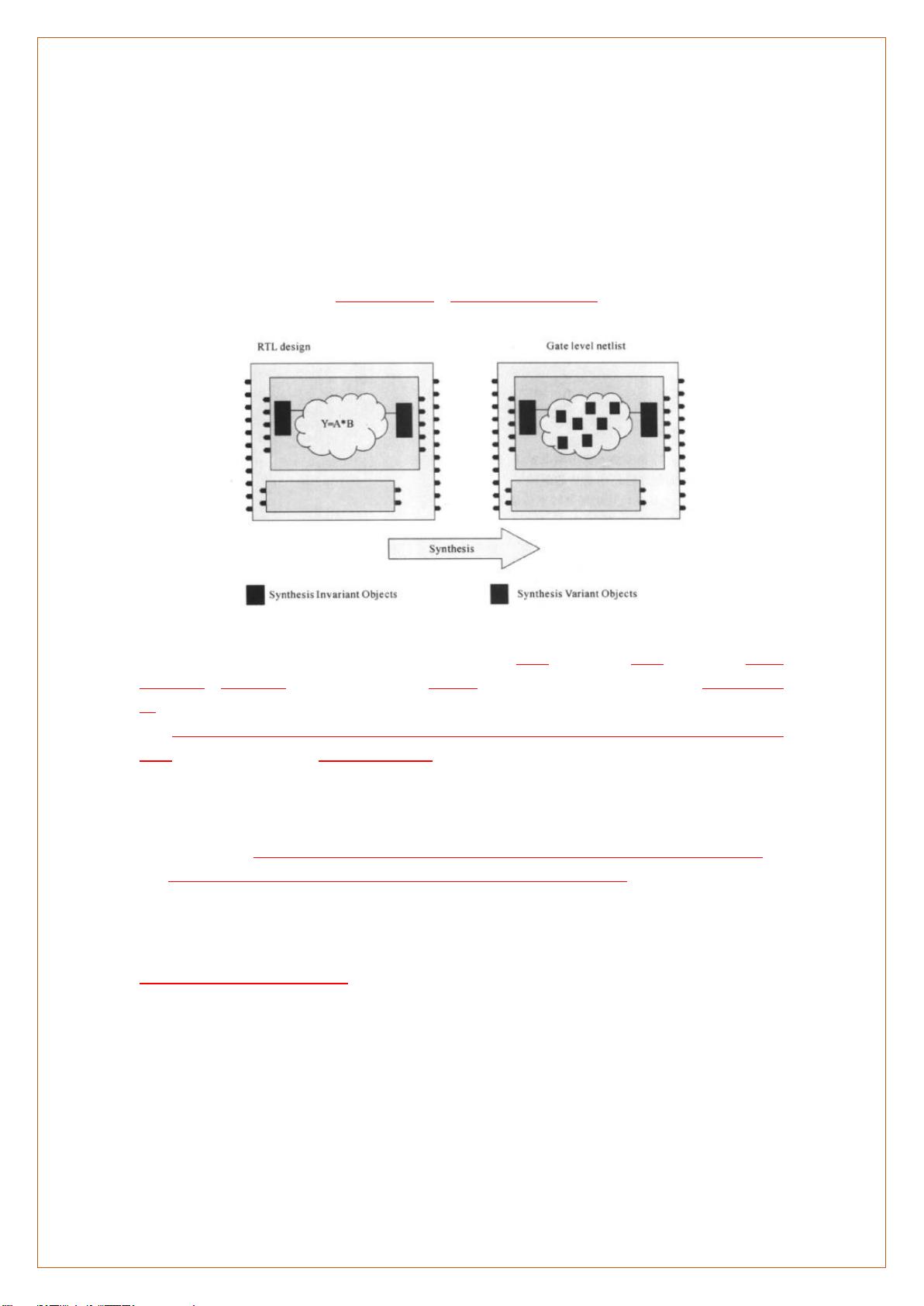

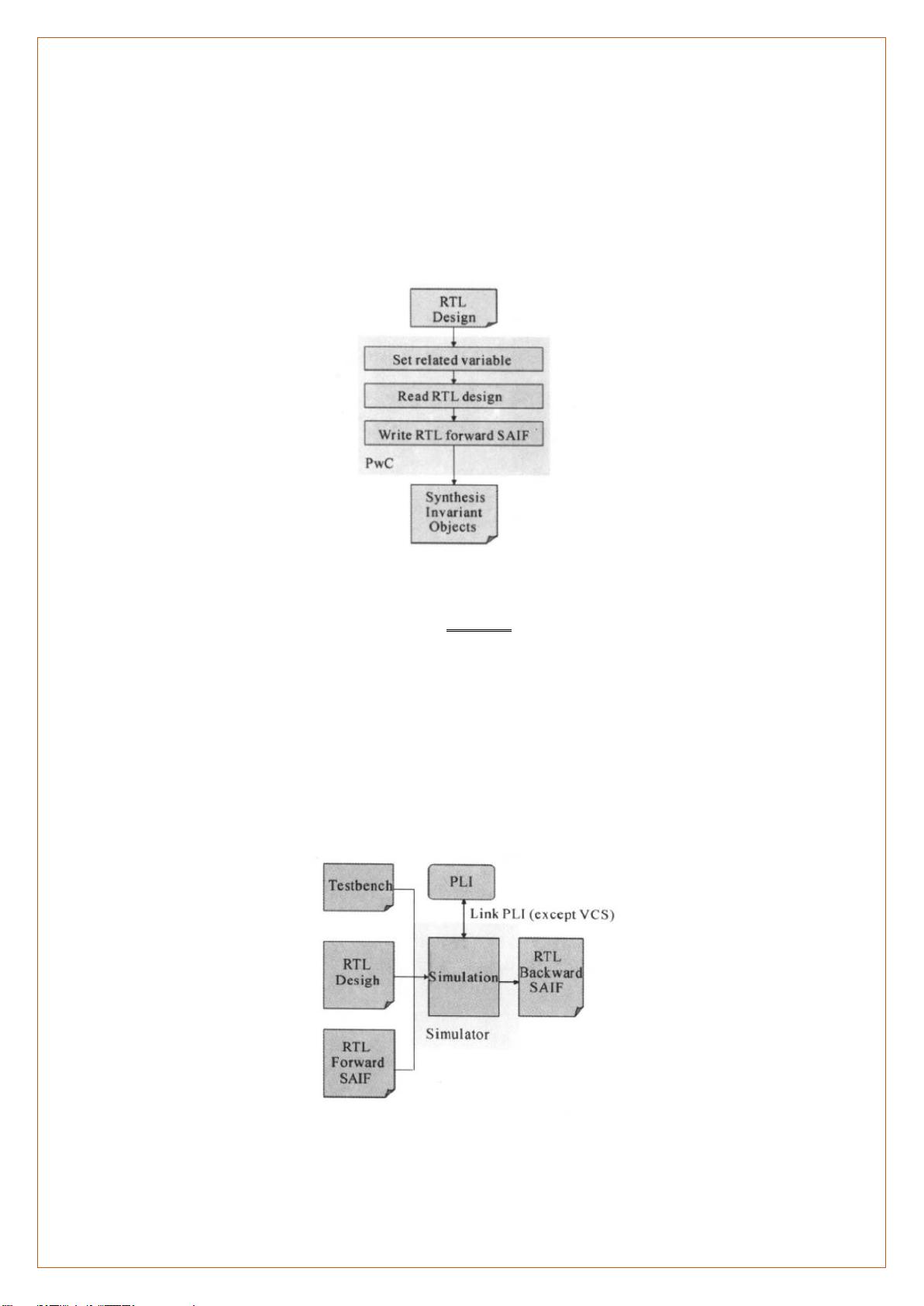

4. 功耗分析与流程:文档还涵盖了使用EDA(Electronic Design Automation)工具进行功耗分析的流程,如利用Power Compiler、Synopsys PrimeTime等工具进行RTL(Register Transfer Level)设计时的功耗评估,以及DC(Delay-Clock Analysis)阶段对电路静态功耗的优化。

5. 低功耗设计与优化:文档提供了实施低功耗策略的具体方法,例如时钟门控、动态电压和频率调节(DVFS)、电路架构优化(如使用低功耗模式、减少冗余逻辑)等技术,以及如何在设计初期就考虑功耗问题,进行精细化的设计迭代。

通过阅读这份文档,学习者能够掌握ASIC低功耗设计的基本概念、关键技术和实际操作技巧,这对于优化芯片设计以降低能耗、延长设备使用寿命具有重要意义。

2019-02-27 上传

2019-04-10 上传

2023-11-19 上传

105 浏览量

2009-01-06 上传

2010-11-16 上传

2022-07-14 上传

2022-09-24 上传

不二崔先生

- 粉丝: 0

- 资源: 3

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布