Xilinx AXI Interconnect v2.1用户指南

需积分: 19 130 浏览量

更新于2024-06-28

收藏 2.67MB PDF 举报

"Xilinx的AXI Interconnect LogiCORE IP产品指南,版本2.1,发布日期为2017年12月20日,文档编号PG059,详细介绍了AXI Interconnect在Vivado设计套件中的应用、规格、设计流程以及示例设计,还包含了升级和调试的相关信息。"

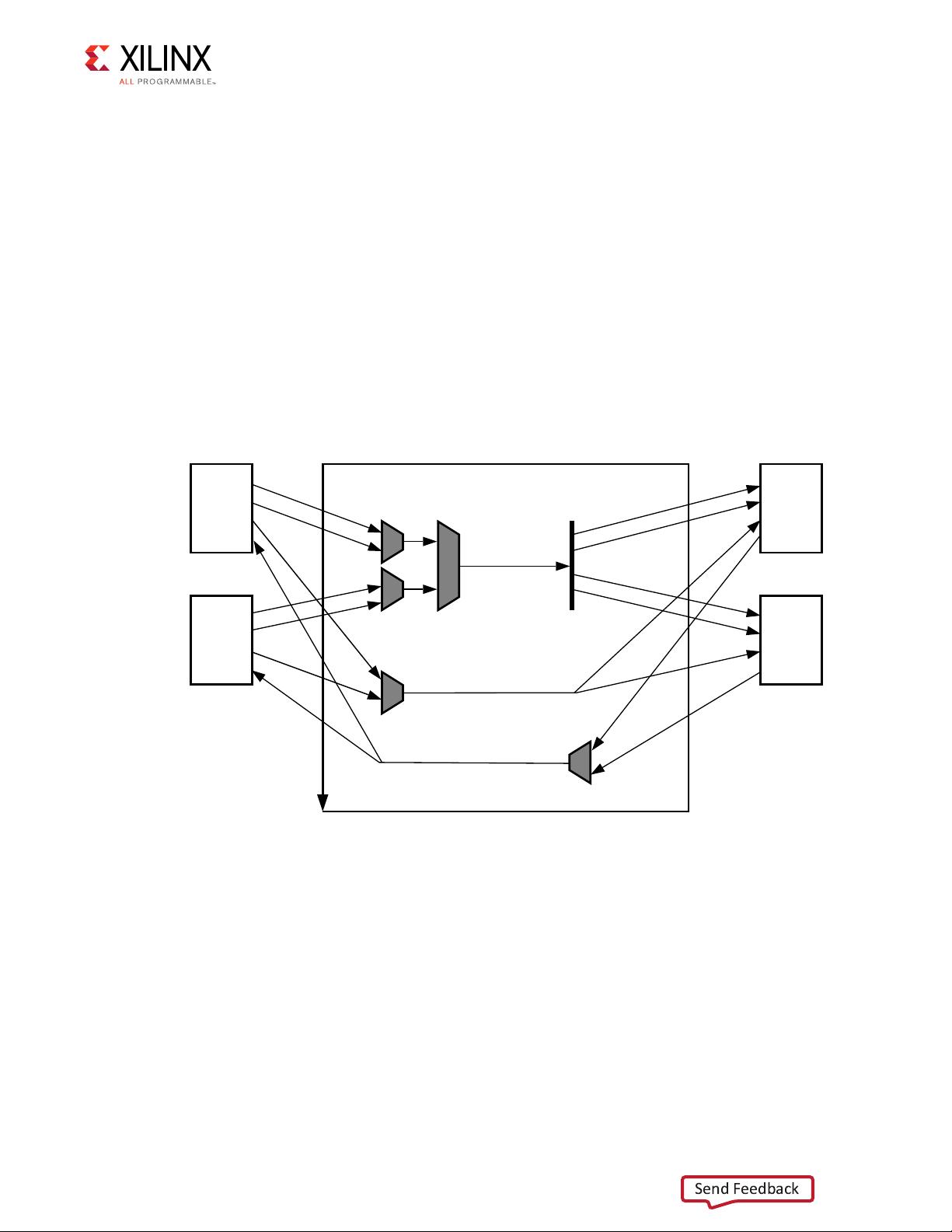

Xilinx的AXI Interconnect是用于FPGA设计的一种关键组件,它提供了一种灵活的方法来连接和管理多个AXI(Advanced eXtensible Interface)协议兼容的IP核。AXI接口是一种高性能、低延迟的通信标准,广泛应用于系统级集成。

该产品指南首先概述了AXI基础设施核心的功能,包括特性摘要,如支持多种AXI协议变体(如AXI4和AXI4-Lite),适用于高速数据传输的应用。AXI Interconnect的主要限制包括连接数量、总线宽度和事务吞吐量等,这些因素可能影响设计的性能和资源利用率。

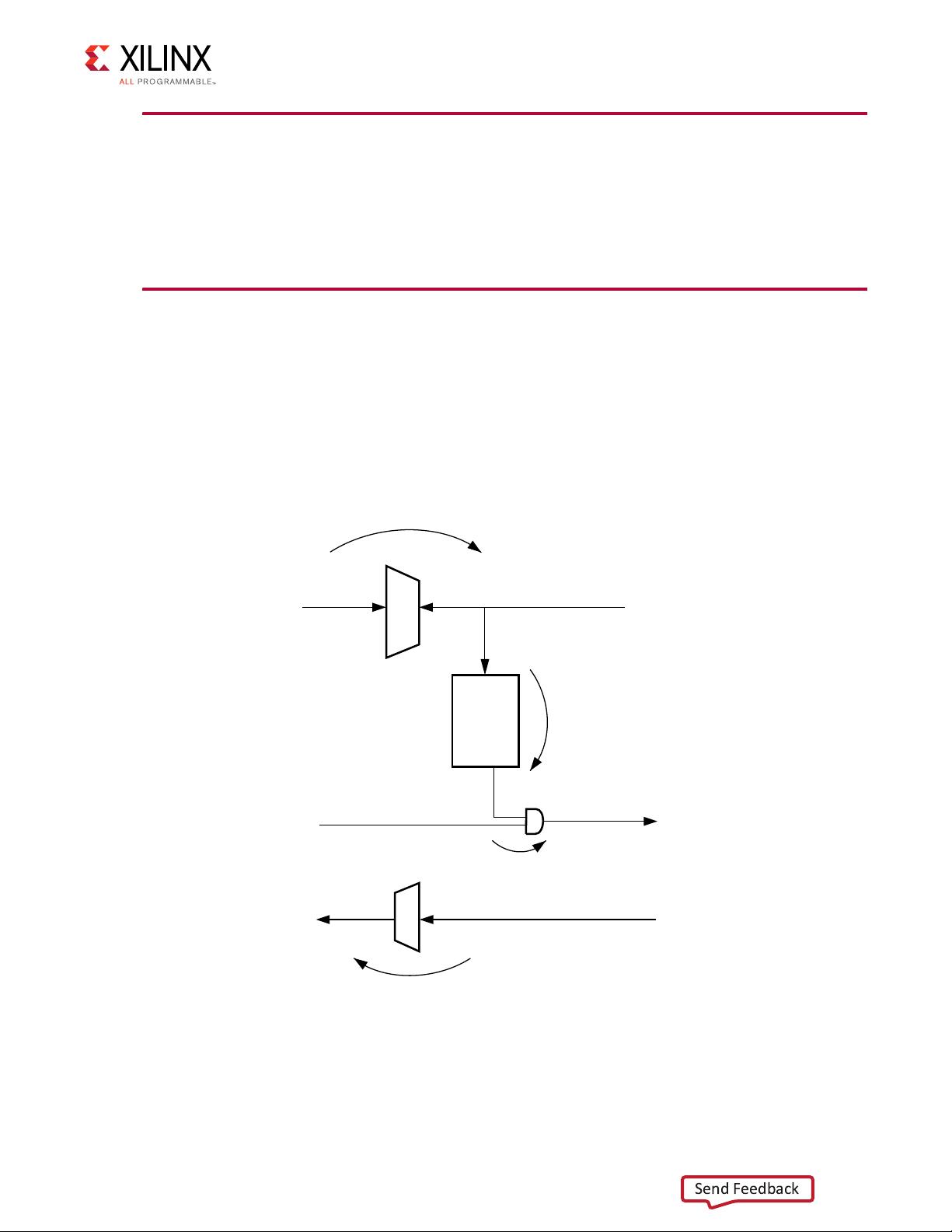

在产品规格部分,详细介绍了使用模型,标准(如AXI4协议规范),以及延迟、最大性能和资源利用情况。延迟部分讨论了数据传输中的时序问题,而最大性能则涉及了在特定FPGA架构下AXI Interconnect可以达到的速度。资源利用章节列出了AXI Interconnect占用的逻辑资源,如触发器、查找表和时钟门控等。

设计流程章节指导用户如何定制和生成AXI Interconnect核心,包括设定设计参数,如总线宽度、优先级策略和仲裁方式。此外,还涵盖了时钟管理和复位信号的配置,这对于确保系统同步和正确操作至关重要。

设计流程还包括约束核心,即设置时序约束,以优化综合和实现过程。之后的章节介绍如何进行仿真,以验证设计的正确性,并提供了合成和实现的步骤,这些都是FPGA设计的关键阶段。

附录部分提供了升级指南,帮助用户从早期版本的CORE Generator System AXI Interconnect或XPS AXI Interconnect升级到Vivado Design Suite中的新版本。此外,还提供了调试方面的帮助,指导用户在遇到问题时如何寻找解决方案。

PG059文档是理解、设计和优化使用Xilinx AXI Interconnect的FPGA系统的宝贵资源,为设计者提供了全面的技术指导和支持。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-29 上传

2024-04-22 上传

2022-09-21 上传

2016-01-17 上传

2019-10-14 上传

点击了解资源详情

咖喱啦啦啦

- 粉丝: 0

- 资源: 2