泰克科技高速信号完整性培训:DDR原理与物理层一致性测试详解

需积分: 49 139 浏览量

更新于2024-07-24

收藏 3.54MB PDF 举报

高速信号完整性是现代电子系统设计中的关键领域,特别是在高速数字集成电路如SDRAM、DDR、DDR II、DDR III的设计和测试中。此培训课程专注于泰克科技(中国)有限公司提供的专业指导,旨在提升工程师对高速信号完整性的理解和实践能力。

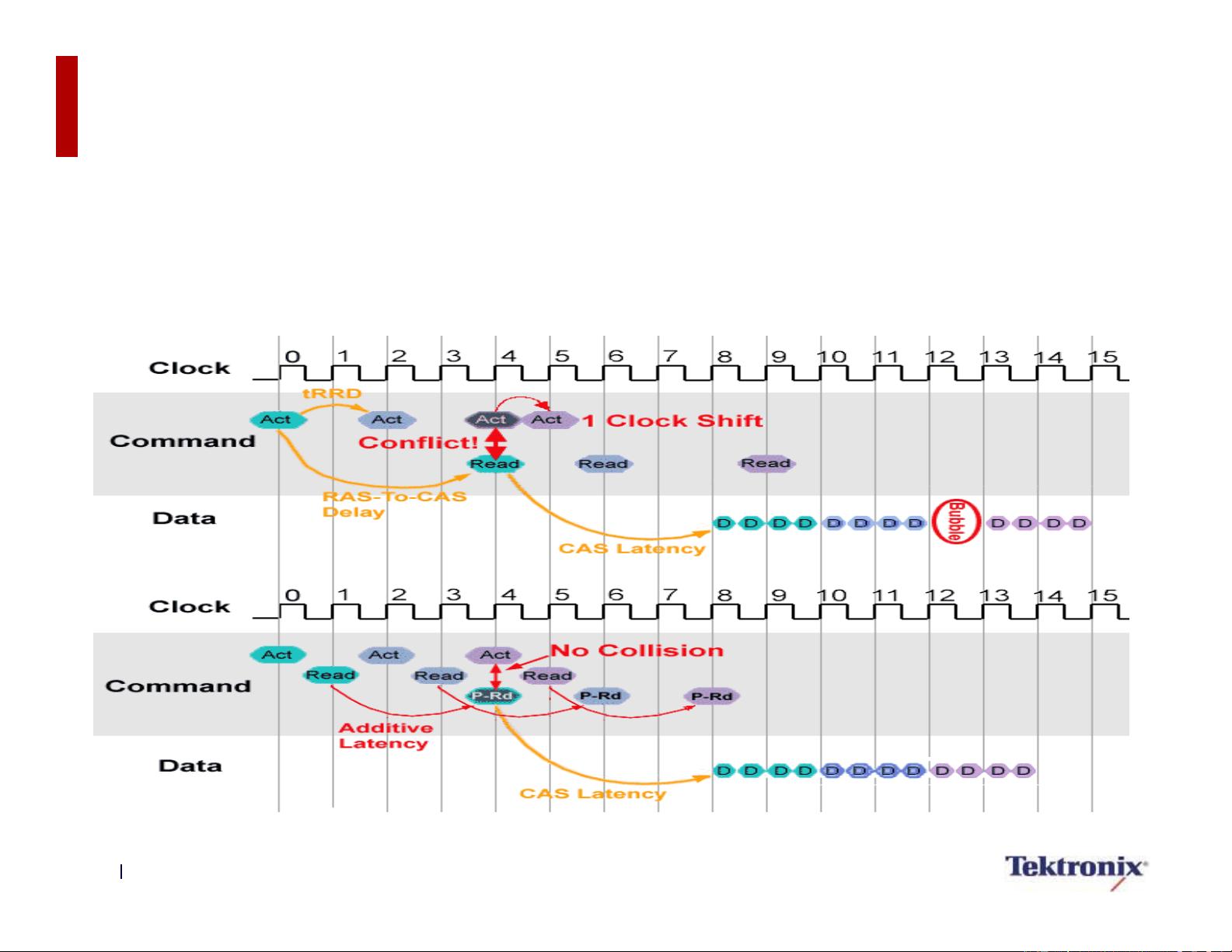

首先,课程介绍了DDR(Double Data Rate SDRAM)系列的发展,从最初的SDRAM到后来的DDR II、DDR III,这些技术的主要区别在于预取(prefetch)能力的增强。DDR II支持4-bit预取,可以同时读取4n个数据;DDR III则进一步提升至8-bit预取,大大提高了数据传输效率。这种技术的进步不仅提升了数据速率(如DDR III的Data Freq达到800MHz),还要求信号完整性工程师具备处理高速信号时钟频率和数据频率的能力,以确保信号质量不受噪声和串扰的影响。

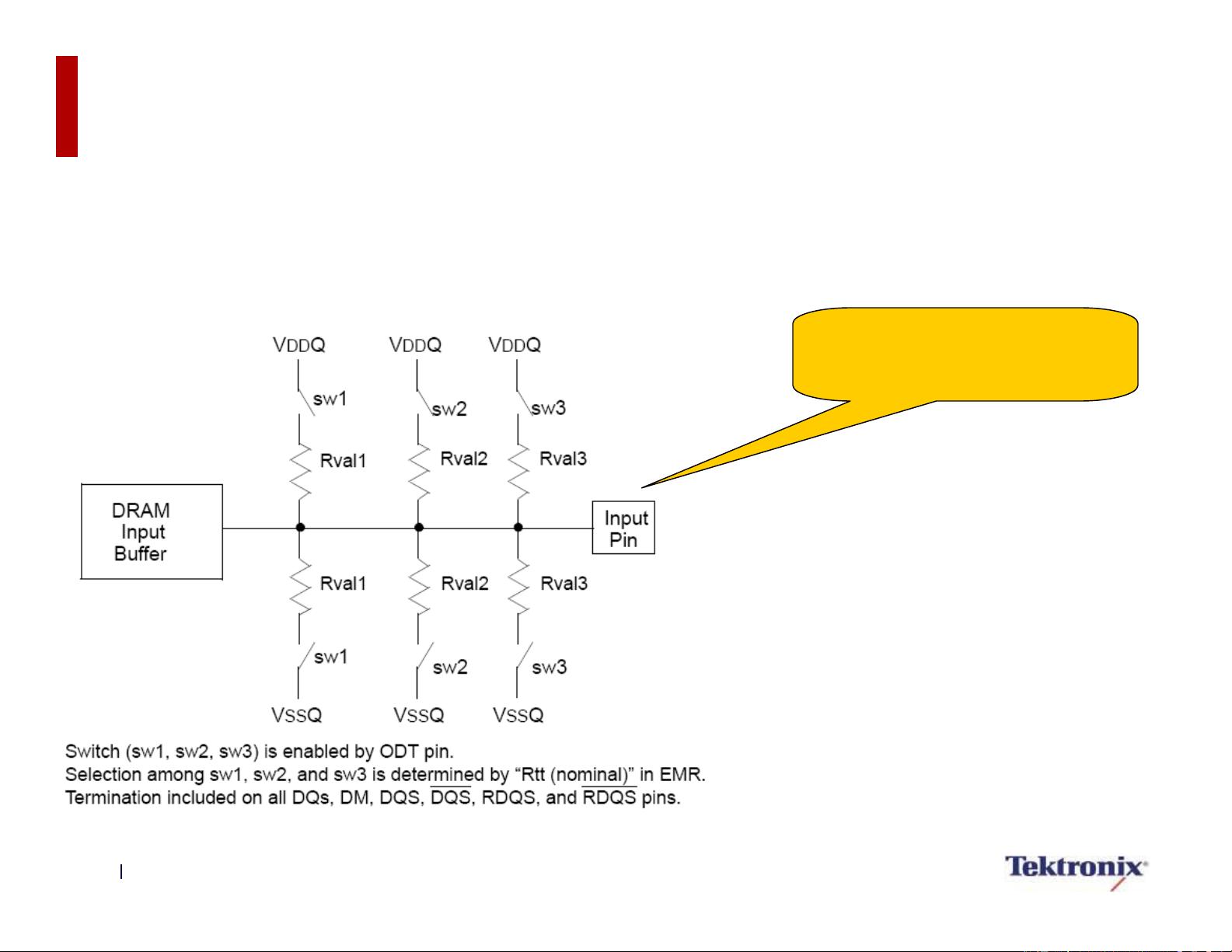

在架构方面,DDR SDRAM采用源同步技术,通过Clock上升沿对Command和Address进行采样,以及DQS(Data strobe)在数据线(DQ)上升沿和下降沿同步采样,减少了由于skew(时延不匹配)导致的误采样问题。源同步机制确保了数据在传输过程中的一致性和准确性,这对于保证系统性能至关重要。

接下来,课程讨论了DDR和DDR II的拓扑结构,包括DDR的单通道设计,而DDR II则引入了更复杂的多银行(banks)和输出设计,如1K列x16K行x4银行x8输出的典型配置,这在DDR IIi的512Mb存储器中得到了体现。这些拓扑结构设计对于理解信号如何在大规模内存模块间流动以及如何优化信号路径以提高信号完整性至关重要。

最后,图像来自Micron Technology, Inc.的示例展示了DDR II的具体布局,有助于学员理解不同组件之间的连接和信号交互方式,这对于设计者来说是理解和解决问题的重要视觉参考。

高速信号完整性工程师培训课程涵盖了DDR系列的基本原理、物理层一致性测试、关键架构特性以及实际设计中的拓扑结构。掌握这些知识对于保证高速数字系统如DDR内存的稳定性和性能具有决定性作用。工程师需要熟练运用这些理论和实践技巧,以应对不断增长的系统复杂性和信号完整性挑战。

2020-09-02 上传

2013-09-09 上传

2009-07-09 上传

2021-07-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

hust0610

- 粉丝: 0

- 资源: 1

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍