同步时序逻辑电路设计实例:序列脉冲检测器

版权申诉

87 浏览量

更新于2024-08-19

收藏 989KB PPTX 举报

6.3同步时序逻辑电路的设计是IT领域中一种关键技能,它涉及根据特定的逻辑需求构建时序电路,以实现预期的功能。在这一节中,主要讲解了设计时序逻辑电路的步骤和实例。

首先,设计时序逻辑电路的一般步骤包括:

1. 理解逻辑要求:根据题目要求明确电路的功能,例如,例6.3.1中的序列脉冲检测器,其目标是在连续接收到110信号时输出1,其他情况下输出0。

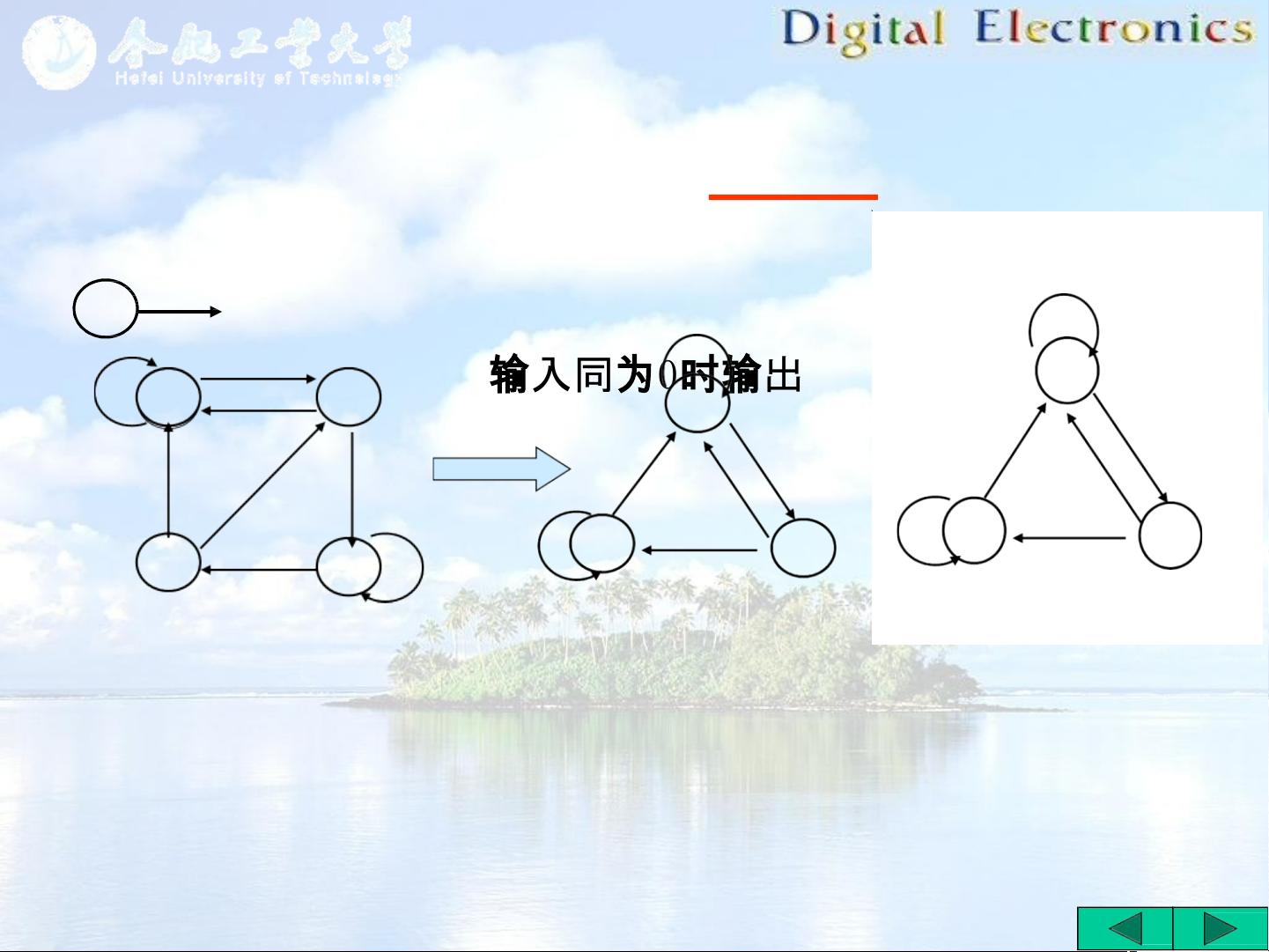

2. 画原始状态图:这是设计过程的基础,通过列举所有可能的输入状态和对应的电路状态,形成状态图,以帮助理解和分析电路的行为。

3. 状态表与状态编码:通过状态表来描述每个状态的输入和输出,然后通过状态编码将状态简化,合并等效状态,以便于后续的电路设计。例如,通过观察输入0和11时的状态转换,合并S0和S3。

4. 确定触发器数量:计算电路状态的总数(M),根据公式2n-1<M<2n,决定需要的触发器数量。在这个例子中,由于有3个状态,需要2个触发器(JK触发器)来存储状态。

5. 驱动方程与输出方程:根据状态表推导触发器的驱动方程,即输入信号如何控制触发器的状态转移。同时,确定电路的输出方程,即触发器状态如何映射到实际的输出信号。

6. 逻辑电路图绘制:最后,根据驱动方程和输出方程,绘制完整的逻辑电路图,确保电路自启动能力和正确的工作流程。

通过这个实例,学习者可以掌握如何将理论知识应用到实际问题中,如如何分析问题、设计电路结构,以及如何利用触发器进行状态控制。同步时序逻辑电路的设计不仅要求精确性,还强调了对逻辑流程的理解和对触发器行为的掌握,这对于开发复杂电子系统至关重要。

2024-09-15 上传

2024-08-19 上传

2022-01-10 上传

2021-11-09 上传

2023-08-29 上传

2022-11-17 上传

2019-08-08 上传

念广隶

- 粉丝: 5w+

- 资源: 6万+

最新资源

- 基于ASP的网站新闻管理系统的设计

- mod_perl编程指南(中文)

- 迈瑞笔试题 软件开发

- Linux内核详细注释

- Cyclone_074641_1.pdf

- 精彩分享:SUN云计算解读

- 计算机仿真技术的讲义

- 高质量C++编程指南 pdf

- 使用 PowerDesigner 进行数据建模

- 基于OpenSSL的嵌入式网络安全通信设计与实现

- 基于OpenSSL的密码支撑平台的研究与开发

- Delphi 6.0数据库深入编程技术 .pdf

- FPGA_PCB管脚同步.Altium Designer Summer 09

- SUN云计算架构介绍白皮书 2009年6月

- Linux系统开发技术详解—基于ARM

- DB2 Express-C快速入门