Zynq ZC706评估板详解与应用概述

需积分: 5 74 浏览量

更新于2024-06-21

收藏 7.16MB PDF 举报

"UG954-zynq zc706评估版是针对Xilinx Zynq-7000 XC7Z045 SoC设计的开发和评估平台,它提供了丰富的硬件功能,包括DDR3内存、PCI接口、以太网PHY、通用I/O和UART接口等。此外,该板卡还支持通过FMC连接器扩展其他功能。用户指南(UG954 v1.8)包含了AXIGPIO v2.0的介绍,这是一个32位的AXI接口通用输入/输出核心,适用于AXI4-Lite接口,具备动态配置、独立重置值等功能,并支持中断请求生成。"

本文将详细阐述Zynq ZC706评估板的关键特性及其在Zynq-7000 SoC开发中的作用,同时深入解析AXIGPIO IP核的功能与应用。

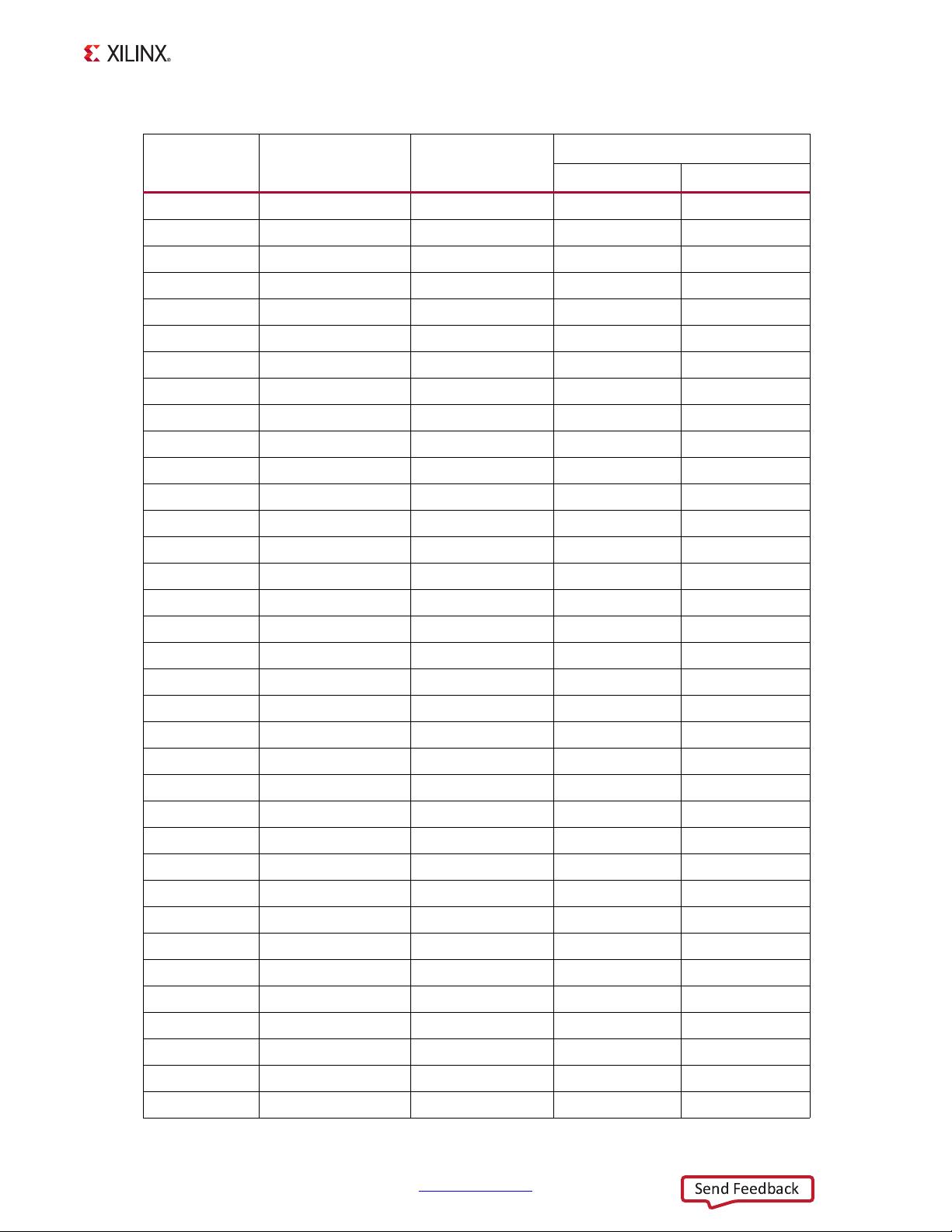

Zynq ZC706评估板是基于Xilinx Zynq-7000 XC7Z045 SoC的开发平台,它的主要设计目标是为工程师提供一个全面的环境来测试和优化针对这款SoC的硬件和软件设计。该板卡配备了多种常用接口,如DDR3 SODIMM内存模块,可以满足高速数据存储需求;四通道PCI接口允许与外部设备进行高速数据交换;以太网PHY接口则提供了网络连接能力;通用I/O接口可以适应各种外设的连接;两个UART接口则用于串行通信。

除此之外,ZC706评估板还特别考虑了扩展性,通过VITA-57 FPGA mezz卡接口,支持FMC(FPGA Mezzanine Card)标准,允许用户根据需要添加LPC或HPC类型的FMC扩展卡,以实现更复杂或特定的应用场景。

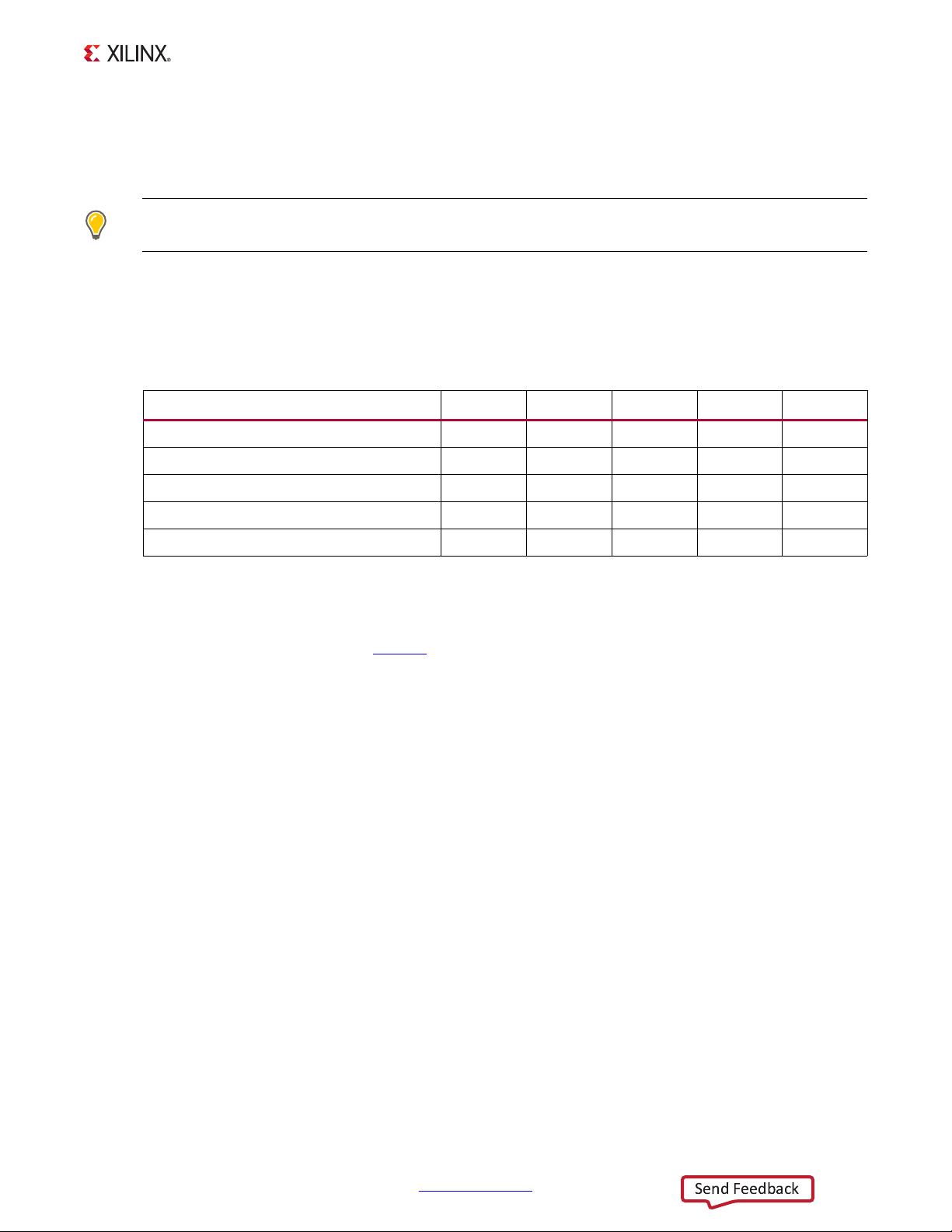

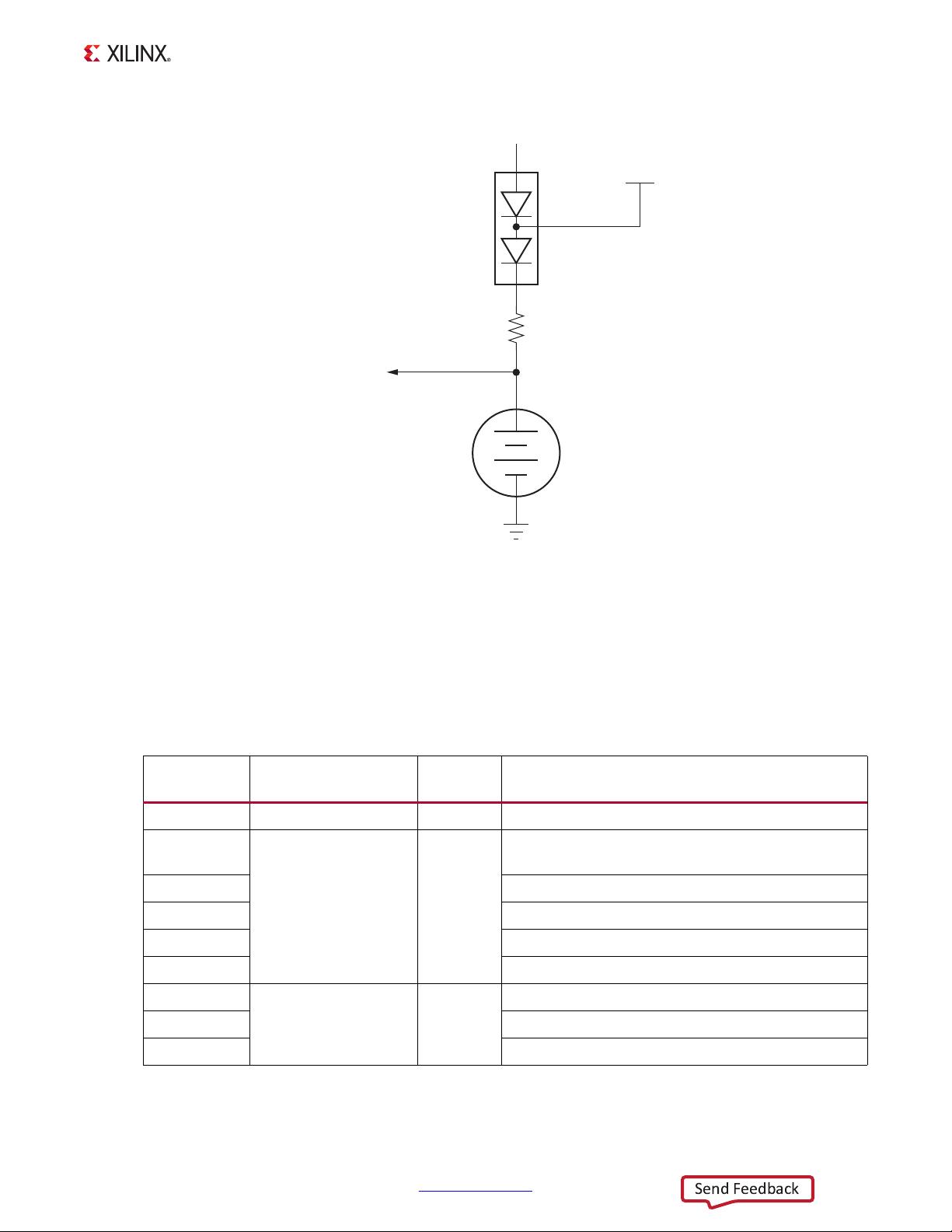

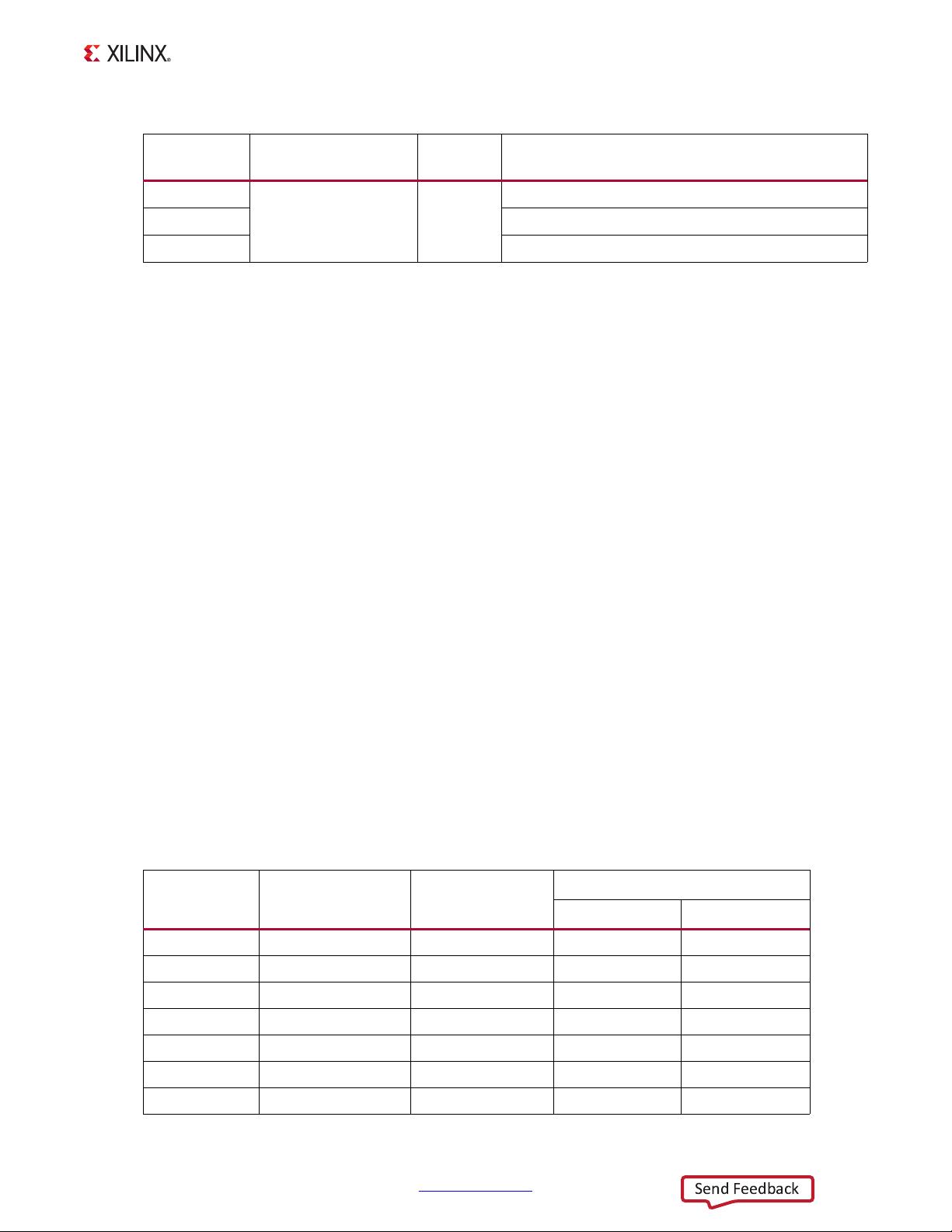

AXIGPIO v2.0是Xilinx的LogiCORE IP,它在ZC706评估板上扮演着重要角色。它是一个32位的GPIO(General Purpose Input/Output)核心,能够通过AXI4-Lite接口与系统通信。此IP核支持单通道或双通道配置,通道宽度可自定义,范围从1到32位。AXIGPIO的核心特点包括:

1. 支持AXI4-Lite接口规范,适合低带宽、低功耗的应用。

2. 可配置的单通道或双通道,灵活适应不同应用场景。

3. GPIO引脚可以动态编程为输入或输出模式。

4. 每个通道可以独立配置,提供定制化的功能。

5. 所有寄存器的每个比特都可以设置独立的复位值,确保系统初始化的灵活性。

6. 具备可选的中断请求生成功能,能根据GPIO状态触发中断,增强系统的响应能力。

在实际设计中,用户可以利用提供的VHDL示例设计,快速理解和集成AXIGPIO IP核,从而在Zynq ZC706评估板上构建复杂的系统。这些设计文件和示例有助于开发者迅速上手,提高开发效率。

Zynq ZC706评估板是Zynq-7000 SoC开发的强有力工具,而AXIGPIO v2.0 IP核则提供了灵活的GPIO接口解决方案。结合两者,工程师可以充分利用Zynq SoC的强大性能和丰富的外设接口,进行高效且具有扩展性的设计。

253 浏览量

626 浏览量

2812 浏览量

338 浏览量

246 浏览量

228 浏览量

547 浏览量

Flowers、Flow

- 粉丝: 1

- 资源: 4

最新资源

- 销售管理系统的论文材料.doc

- UML分析与设计.pdf

- 超市销售管理系统.doc

- 用Eclipse软件更新方法安装JSEclipse

- Flex 3 Cookbook 中文版V1

- petstore数据模型分析

- The big SoftICE howto.pdf

- 微软原版教材2555A课程(带翻译).pdf

- javascript高级教程

- 进销存系统 详细设计

- Transfering-Data-between-SAS-and-Stata

- SD Specifications version2.0

- 中南大学 先进控制 大爱迪达

- JasperRepor iReport整合的Web报表开发

- asp.net2.0数据库入门经典DOC格式

- pso算法基本概念和实现