CoolRunner-II UART接口详解:发送、时钟与接收逻辑

117 浏览量

更新于2024-08-31

收藏 285KB PDF 举报

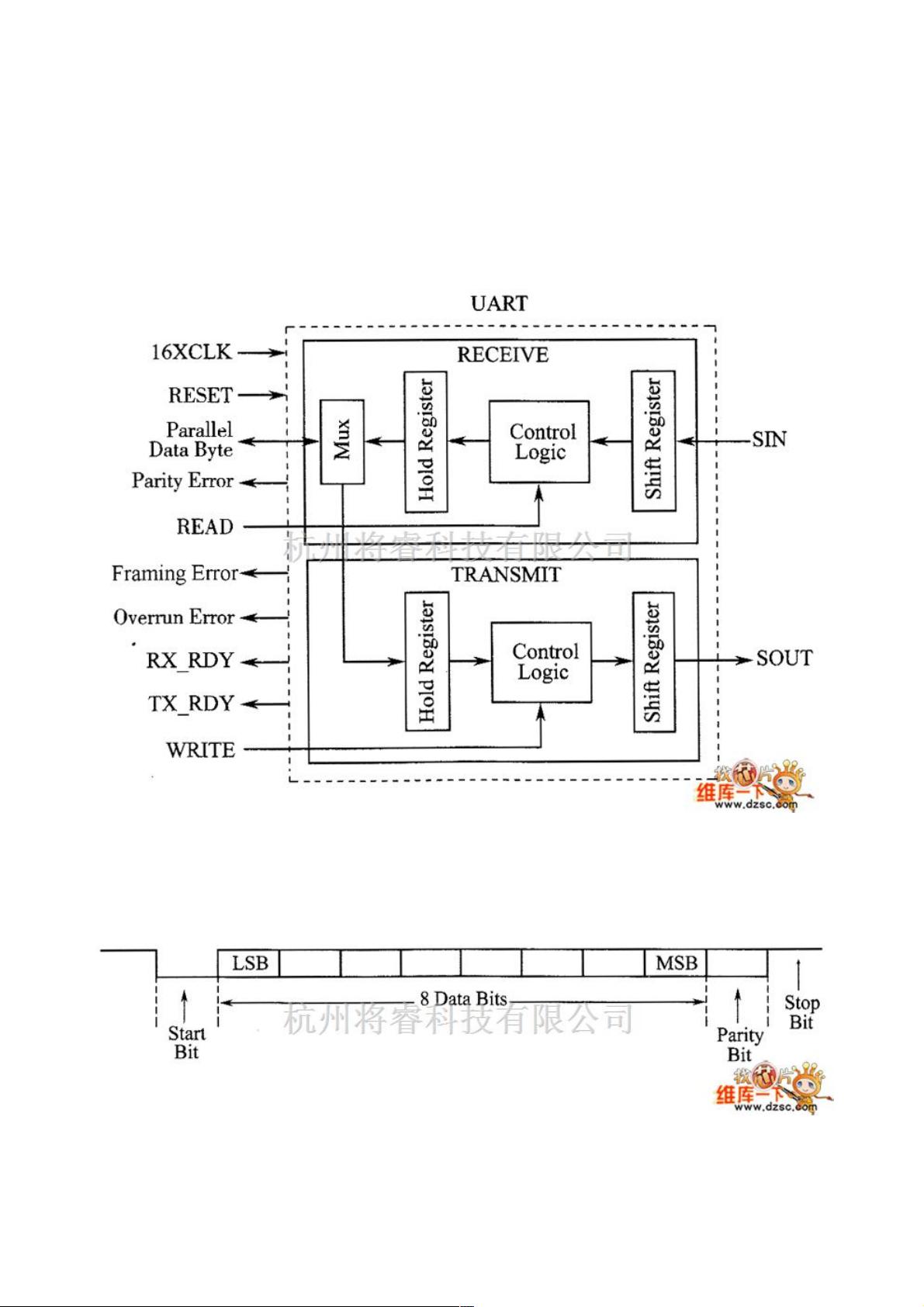

CoolRunner-II的UART部分接口是一个关键的通信组件,用于串行通信,特别是在微处理器和微控制器之间的数据交换。接口的核心组成部分包括:

1. **UART接口框图**:

UART接口由8位并行数据总线组成,其中输出SOUT支持奇偶校验功能,确保数据传输的准确性。SOUT的输出格式经过精心设计,如图1和图2所示。

2. **发送逻辑**:

- 发送逻辑与处理器的数据总线和读写控制线紧密配合。当Write信号为低时,发送逻辑会从总线读取数据并存入保持寄存器,然后等待Write信号释放来触发发送过程。

- 发送过程中,数据按照串行形式通过SOUT发送,如图3所示,涉及到发送保持寄存器、控制逻辑以及移位输出逻辑。

3. **时钟分频模块**:

此模块负责将系统时钟分频,生成与波特率匹配的发送时钟TXCLK,通过3位计数器实现,如图4所示。每当计数器清零时,TXCLK会发生翻转,驱动数据的正确序列化。

4. **移位输出逻辑**:

包括STARTTRANSMIT和SHIFTOUT逻辑,它们控制发送过程的开始、数据的移位以及奇偶校验位的处理。当paritycycle信号有效时,奇偶校验位会被输出,之后是STOPBIT,txdone标志也会被置位。

5. **接收逻辑**:

UART接收逻辑针对IrDA模块接收到的SIN信号进行解码,该信号以起始位开始,持续8个时钟周期。接收数据被解码后,会传输到微处理器的数据总线上,如图6所示。

6. **控制信号检测**:

DETECTEDGE检测器用于捕捉SIN信号的边沿,确保正确的帧同步和数据接收。

CoolRunner-II的UART部分接口设计考虑到了数据的高效、准确传输,以及与外部设备的兼容性,是构建通信链路的重要组成部分。理解并掌握这些细节对于正确配置和使用UART接口进行通信至关重要。

2020-11-17 上传

2023-08-16 上传

2023-04-19 上传

2023-06-12 上传

2024-07-05 上传

2023-06-09 上传

2023-07-27 上传

2024-09-27 上传

weixin_38667835

- 粉丝: 6

- 资源: 937

最新资源

- 批量文件重命名神器:HaoZipRename使用技巧

- 简洁注册登录界面设计与代码实现

- 掌握Python字符串处理与正则表达式技巧

- YOLOv5模块改进 - C3与RFAConv融合增强空间特征

- 基于EasyX的C语言打字小游戏开发教程

- 前端项目作业资源包:完整可复现的开发经验分享

- 三菱PLC与组态王实现加热炉温度智能控制

- 使用Go语言通过Consul实现Prometheus监控服务自动注册

- 深入解析Python进程与线程的并发机制

- 小波神经网络均衡算法:MATLAB仿真及信道模型对比

- PHP 8.3 中文版官方手册(CHM格式)

- SSM框架+Layuimini的酒店管理系统开发教程

- 基于SpringBoot和Vue的招聘平台完整设计与实现教程

- 移动商品推荐系统:APP设计与实现

- JAVA代码生成器:一站式后台系统快速搭建解决方案

- JSP驾校预约管理系统设计与SSM框架结合案例解析