"XilinxFPGA高速串行接口设计与实现研究:LVDS和CML信号的优化"

需积分: 17 21 浏览量

更新于2024-02-02

收藏 2.95MB DOC 举报

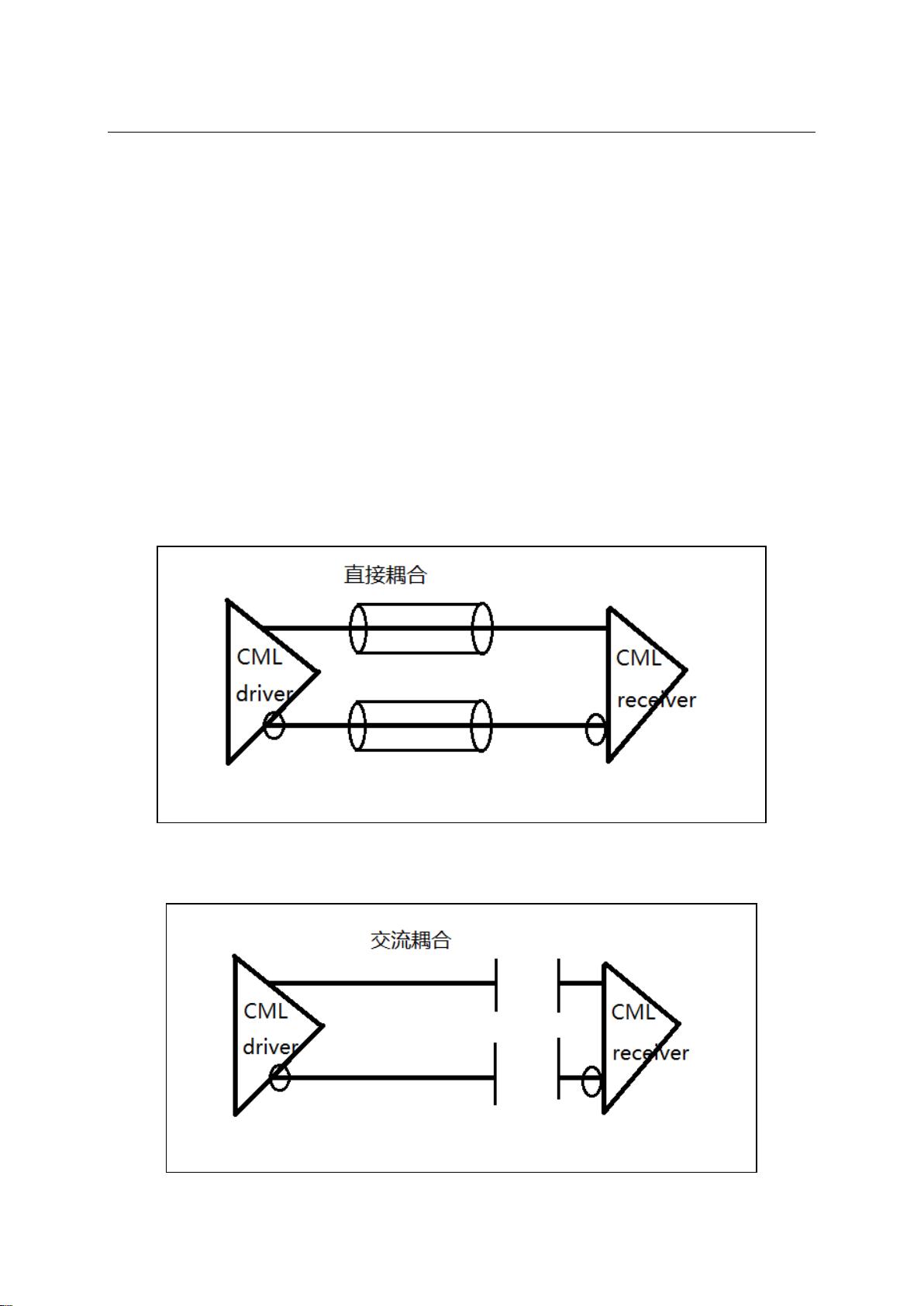

本文基于Xilinx FPGA高速串行接口进行了设计与实现的研究。在传输率方面,由于时钟抖动、扭曲、队列同步和串扰噪声等非理想因素的存在,对于进一步提高并行传输率面临着巨大的挑战。因此,串行传输成为了在深亚微米主要选择使用的高速数据传输系统。为了实现高速信号传输并节约电能和降低成本,在串行传输系统中更倾向于使用低摆幅模式的LVDS和CML作为低电压、小摆动、差分信号的传输方式。这两种传输方式被广泛应用在PCI、快递网络物理层和高速SERDES电路中。然而,LVDS的传输率只能达到3Gbps,无法满足5Gbps以上的高速PCI应用需求。

为了满足高速PCI的要求,本文研究了伪标准的LVDS 121(PLVDS)和CML的启动界面的设计。通过对传输信号的理论分析,非理想因素的考虑以及传输线的行为的研究,本文提出了考虑高速串行传输系统的电路级和版图级设计。在PLVDS和CML收发器电路的设计中,本文还提出了改进方案以解决无歪斜单端差挠度问题,提高PLVDS收发电路的性能并加速管的改进。同时,本文还提出了电平转换电路的设计方案,能够使信号快速切换到低水平或高水平,而无需进行后续电路的调整,以降低延迟。

通过对高速串行传输系统的研究,本文的贡献主要包括以下几个方面:首先,本文对传输信号的理论进行了分析,充分考虑了非理想因素和传输线的行为,使设计更加符合实际应用需求;其次,本文设计了PLVDS和CML的启动界面,并提出了改进方案,提高了传输系统的性能;最后,本文还设计了电平转换电路,实现了信号快速切换和延迟降低的目标。

综上所述,本文基于Xilinx FPGA高速串行接口进行了设计与实现的研究。通过对伪标准的LVDS 121和CML的启动界面进行设计研究,本文提出了相应的改进方案,使得高速串行传输系统更加符合实际应用需求。本文的研究成果具有一定的实际应用价值,并为今后的相关研究提供了参考和借鉴。

102 浏览量

1013 浏览量

210 浏览量

399 浏览量

182 浏览量

239 浏览量

智慧安全方案

- 粉丝: 3851

最新资源

- 嵌入式Linux应用程序开发详解-入门篇

- 多媒体数据挖掘:系统框架与方法探索

- JavaScript基础与常用语句大全

- Microsoft Media Transfer Protocol (MTP) 扩展规范

- 深入解析FAT文件系统:FAT12, FAT16, FAT32

- 搜索引擎优化SEO详解:通往成功的关键步骤

- 软件世纪的变革力量

- Vim入门指南:实战提升编辑技能

- Ant开发指南:入门与进阶

- 掌握PHP基础:语言与平台、数据类型及高效编程

- 信息系统项目管理中知识管理的模糊评价实证研究

- NET-SNMP5.3.2安装与配置实战指南

- Intel IA-32架构开发手册:基础与特性

- 配电工区作业资料管理系统软件维护手册

- C++泛型编程深度探索:《C++Templates全览》解析

- 精通J2EE:Eclipse、Struts、Hibernate与Spring整合实战