异步FIFO设计:结构、难点与解决策略

需积分: 9 112 浏览量

更新于2024-09-15

收藏 126KB DOC 举报

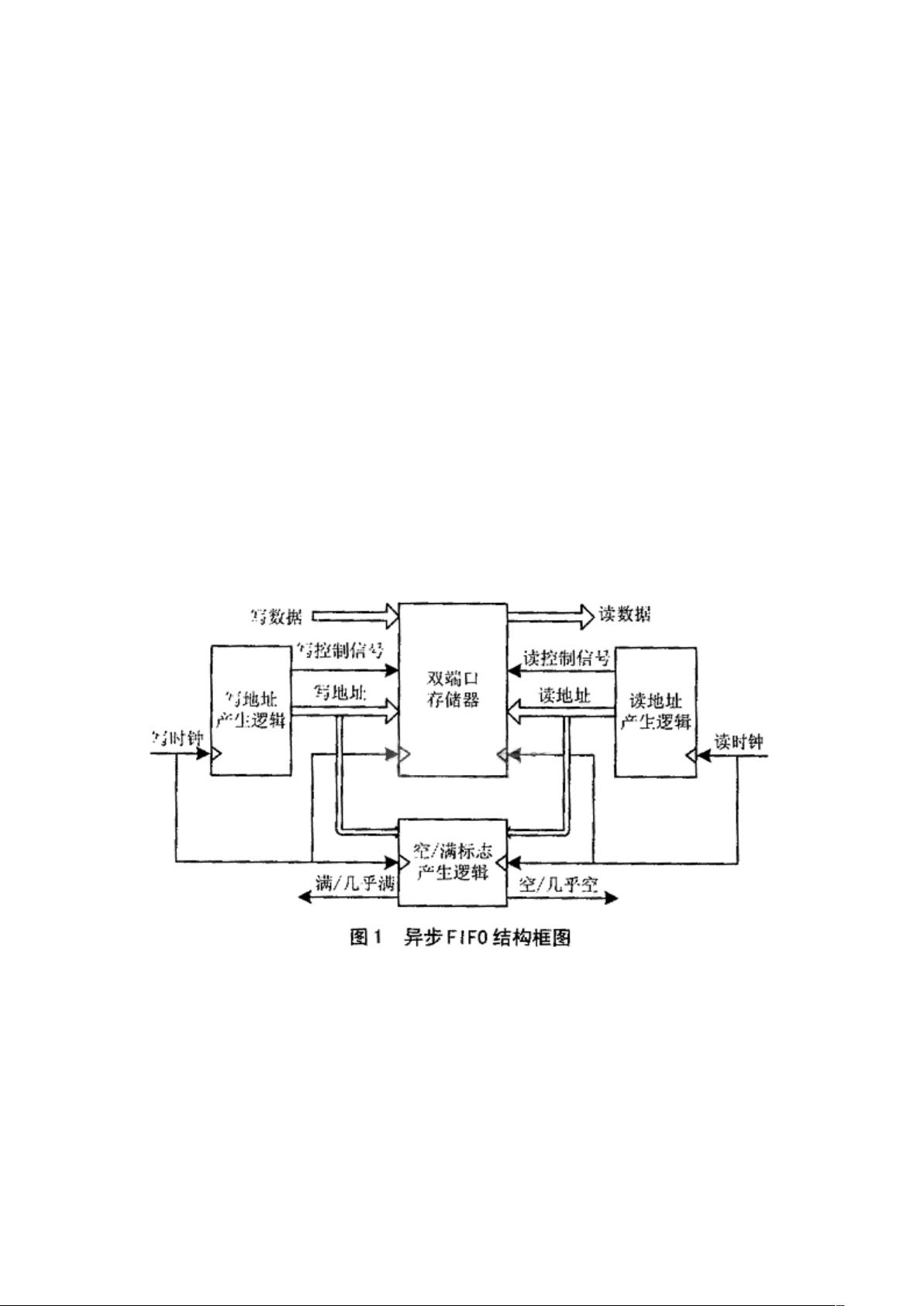

异步FIFO结构及FPGA设计文档详细介绍了异步FIFO的概念、应用以及其实现中的挑战。异步FIFO作为一种关键的数据缓冲机制,在多时钟域系统中起着至关重要的作用,它能够在不同时钟系统之间高效地存储和传输实时数据,常见于网络接口和图像处理等领域。

异步FIFO的核心结构包括两个独立的时钟域:读时钟域和写时钟域,通过双端口RAM实现数据的读写操作。设计难点主要体现在两个方面:首先,异步时钟可能导致触发器产生亚稳态,即寄存器在时钟边缘接收信号时无法稳定状态,这需要满足setup/hold时间要求以确保数据正确存储。其次,如何设计空、满以及几乎满的控制信号,以避免数据溢出或丢失,是另一个挑战。

为解决这些问题,文档提出了一种新颖的电路结构。对于亚稳态,通过精确的时钟管理和有效的数据采样策略,如采用适当的时钟分频、预分频或者使用触发器的双边缘触发模式,来减少亚稳态发生的可能性。对于空/满信号的控制,通常采用比较读写地址的方式来判断FIFO的状态,通过设置合适的阈值和检测机制,确保正确的数据传输和存储。

在设计过程中,作者进行了综合仿真和FPGA实现,以验证新电路结构的有效性和性能。这包括了对电路的静态和动态行为的模拟,以及在实际硬件平台上的功能验证,以确保异步FIFO能够在实际应用中表现出高可靠性和高速度。

总结来说,本研究不仅深入探讨了异步FIFO的设计原理,还提供了实用的解决方案,为FPGA设计者提供了一套完整的方法论,以应对异步接口设计中的复杂性,特别是在处理异步时钟和亚稳态问题上。通过这种方法,可以有效地提高系统的稳定性和数据传输效率。

2014-06-03 上传

107 浏览量

2021-09-16 上传

2011-03-07 上传

2019-09-05 上传

2022-06-12 上传

2013-04-03 上传

2010-06-04 上传

2022-11-21 上传

nizhenniu2012

- 粉丝: 0

- 资源: 5

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码