CMOS电路电气行为分析:数字逻辑设计Lec03

版权申诉

190 浏览量

更新于2024-07-03

收藏 1.65MB PPT 举报

"数字逻辑设计及应用教学英文课件:Lec03.ppt,由陈岩教授在2011年春季于电子科技大学讲授,主要涵盖了数字逻辑设计的基础概念和CMOS电路的电气行为。"

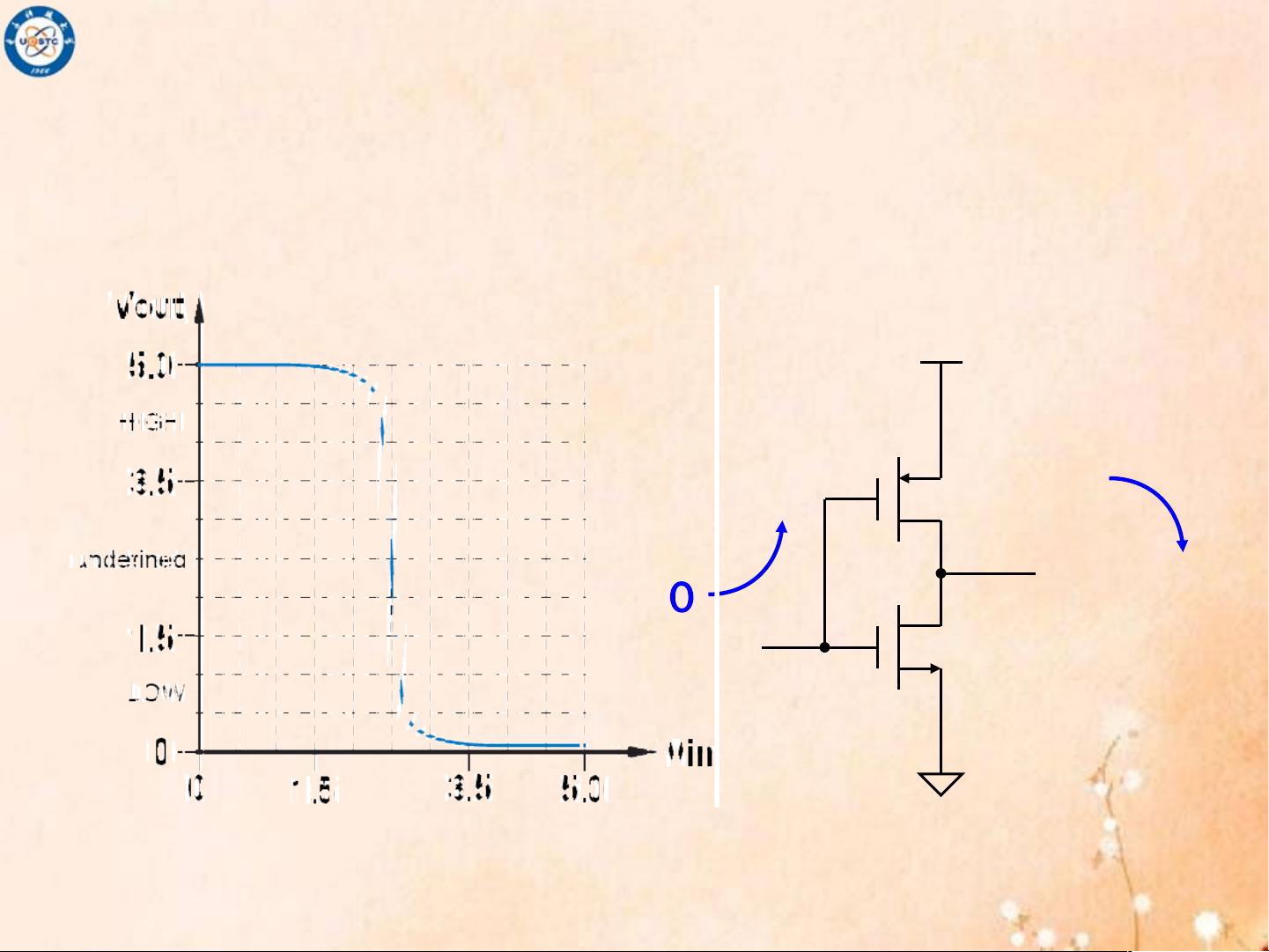

这篇课件是关于数字逻辑设计及应用的,主要针对CMOS(互补金属氧化物半导体)电路的电气特性进行讲解。首先,上一堂课的内容回顾了正逻辑和负逻辑的概念,以及CMOS逻辑的工作原理。提到了NAND、NOR、AOI(与或非门)和OAI(或与非门),并指出对于n输入门来说,通常需要2n个晶体管来构建。还讨论了传输门、三态门、漏极开路门以及施密特触发电路等关键逻辑门类型。

接着,课程进入了CMOS电路的电气行为分析,这是数字逻辑分析的重要部分。数字分析依赖于电路在特定工作条件下的表现,包括电源电压、温度、输入信号质量、输出负载等。为了确保电路满足规格,需要进行一些“模拟”分析,如检查扇入(fan-in)和扇出(fan-out)规格,以及进行时序分析,确认建立时间和保持时间。

课件详细阐述了以下几点:

1. 逻辑电压水平:定义了逻辑高和逻辑低的电压阈值,这些阈值决定了电路如何正确识别输入和输出状态。

2. 直流噪声容限:这是衡量电路在噪声干扰下仍能保持稳定工作能力的指标。

3. 扇出:描述了一个逻辑门能驱动的其他负载(例如,其他门)的数量。扇出能力直接影响到电路的速度和功耗。

4. 速度:电路执行逻辑操作的速率,受制于晶体管开关速度和布线延迟等因素。

5. 功耗:电路在运行时消耗的能量,包括静态功耗(即使在无信号变化时也存在的)和动态功耗(由信号切换引起)。

6. 噪声:在电路中引入的随机电信号,可能会影响逻辑状态的准确读取。

7. 静电放电(ESD):当带电物体接触电路时可能会发生的瞬时大电流,对电子设备造成损坏。

这一系列内容为理解数字逻辑系统的设计和性能提供了基础,是学习数字集成电路和微电子技术的关键部分。通过深入理解这些概念,学生能够更好地设计和优化CMOS电路,以满足特定的性能和功耗需求。

2022-06-29 上传

2021-09-21 上传

2022-06-29 上传

2022-06-16 上传

2021-09-21 上传

智慧安全方案

- 粉丝: 3836

- 资源: 59万+

最新资源

- growth-record:学习各种语言和技术的过程记录

- Band-Playlist:一个简单的工具,可为您的果酱会议管理乐队的播放列表。 全部在Angularjs + Firebase中。 应用程序可以离线工作

- kiri-web:基里页面

- johnmansson.github.io:托管

- Druid源码(apache-druid-0.22.1-src.tar.gz)

- 基于Swing+jdbc+mysql的Java图书管理系统.zip

- 教育门户

- joshschmelzle:你好! 我是乔希

- 行业文档-设计装置-一种切葱花专用刀具.zip

- mondora-iron-router-rest-auth:IronRouter插件(可选)对服务器路由进行身份验证

- CloudComputingProject1SingleInstance

- dotandbox:点和盒游戏

- 如何使自己的程序自动更新(在线更新).zip

- airtable-lite:轻型安全的Airtable API客户端

- 广东工业大学 数据库课程设计.zip

- notocjk:适用于Android设备的NotoSansCJK和NotoSerifCJK完整补丁