LVDS原理详解:低电压差分信号技术与高速应用

需积分: 9 15 浏览量

更新于2024-09-08

收藏 206KB PDF 举报

LVDS (Low Voltage Differential Signaling) 是一种专为高速数据传输而设计的信号技术,其中文名称为低电压差分信号。LVDS的核心理念是通过使用低电压、低电流的差分信号,实现高效、低噪声和低功耗的高速数据传输。LVDS传输速率通常可以达到155Mbps以上,甚至超过655Mbps,理论上极限速率可达1.923Mbps。

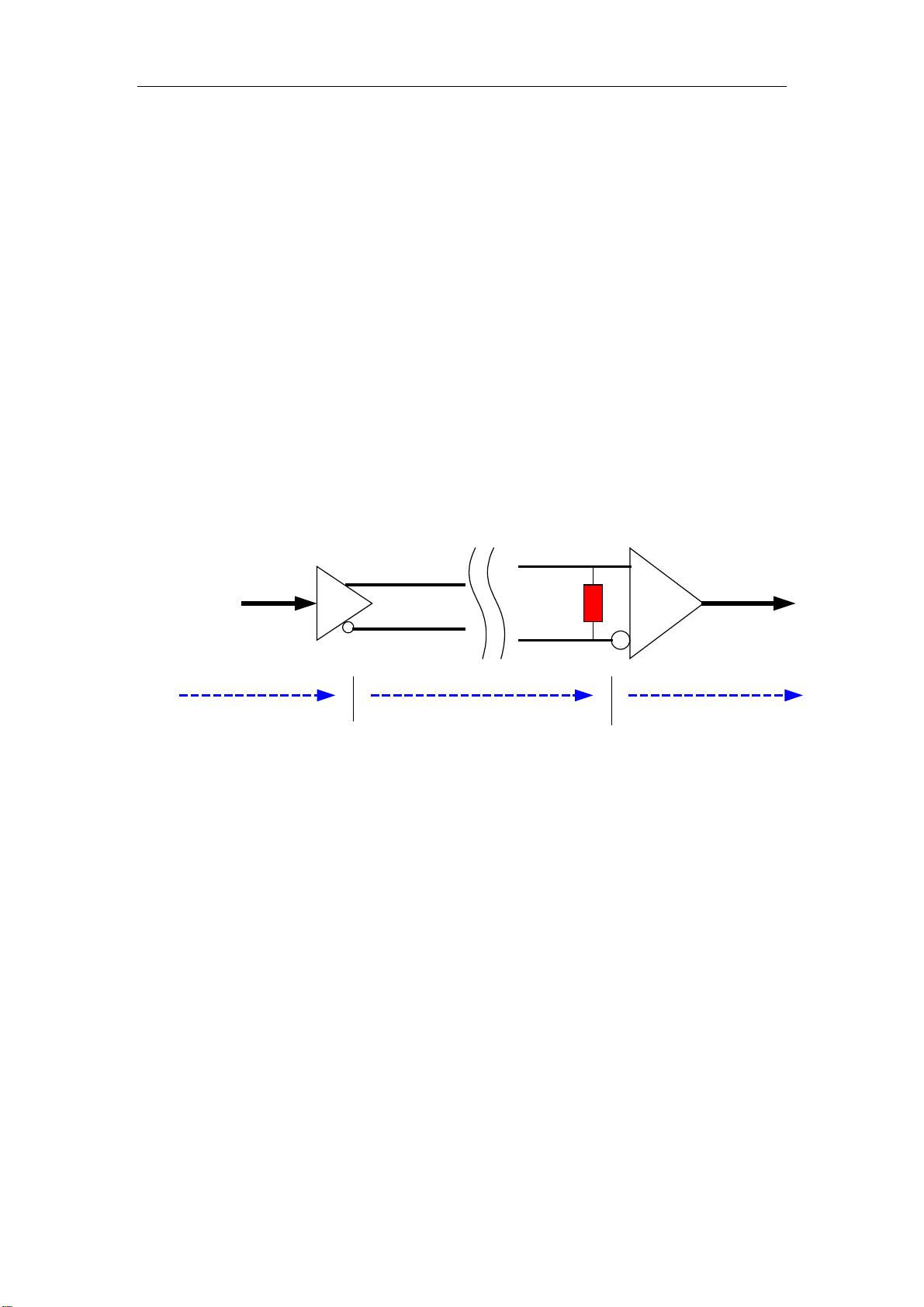

LVDS信号的传输系统主要包括三个组成部分:差分信号发送器、差分信号互联器以及差分信号接收器。发送器负责将非平衡的TTL(Transistor-Transistor Logic,晶体管逻辑)信号转换为平衡的LVDS信号,常见的器件如DS90C031。接收器则是将平衡的LVDS信号转化为非平衡的TTL信号,例如DS90C032。互联器由连接线(如电缆或PCB走线)和终端匹配电阻构成,根据标准(如IEEE),匹配电阻通常设置为100欧姆,但也可根据需求调整为120欧姆。

LVDS信号的特点显著,它采用1.2V偏置电压,具有大约400mV的摆幅。驱动器通过恒定的电流源(约3.5mA)驱动差分线对,大部分电流流经100欧姆或120欧姆的终端电阻,导致接收端产生约350mV至420mV的电压变化。这种设计允许LVDS在逻辑电平变化时表现出更快的速度,从逻辑0到逻辑1的电平转换时间较TTL信号短,特别适合于高速数据传输,如在微电子设计中处理快速变化的信号。

LVDS的低压特性使其能有效降低功耗,这在现代电子设备中尤为重要,特别是在电源效率和能耗管理方面。与PECL(Positive Emitter-Coupled Logic,正发射极耦合逻辑)等其他电平标准相比,LVDS在满足高速性能的同时,提供了更经济和环保的解决方案。因此,LVDS在许多应用领域,如计算机主板、通信系统和工业自动化中得到了广泛应用,是现代电子设计中的关键技术之一。

31277 浏览量

1357 浏览量

点击了解资源详情

547 浏览量

223 浏览量

408 浏览量

436 浏览量

337 浏览量

2023-02-08 上传

HTeeKING

- 粉丝: 0

最新资源

- C++ QT GUI第二版完整源码解析与应用

- Java代码实训4-2项目实战分析

- Emacs编译调度工具Emaci的介绍与应用

- 基于Linux平台的QT点菜系统架构及功能解析

- 全栈网上购物系统开发资源包

- C++3D程序中的矩阵关联技术演示

- 绿色磨砂玻璃背景iOS风格PPT模板下载

- BerryMail_QQ2009第三版:7130黑莓稳定键盘增强版

- React示例项目:从开发到高质量生产部署的完整过程

- 晓晓播放器:基于微软组件与C#的音乐播放解决方案

- Android开发:实时获取并显示时间、小时、分钟及秒

- C++实现九层图书馆电梯系统模拟

- 解决32位/64位兼容问题的Hadoop-2.6.5编译资源

- 微软雅黑字体压缩包介绍:包含轻体、常规与粗体

- 公司内部J2EE框架源代码分享:Struts+Hibernate架构

- 最新免费USB杀毒软件USBCleaner6.0使用体验