Design Compiler电路综合详解

"dc使用中文版(比较详细)——深入理解Design Compiler在集成电路设计中的应用"

Design Compiler是Synopsys公司的旗舰级电路综合工具,它在电子设计自动化(EDA)领域扮演着至关重要的角色。本资源主要介绍了Design Compiler在中文环境下的详细使用,帮助用户理解和掌握如何将高级设计语言(HDL)描述的电路转换成基于特定工艺库的门级网表。

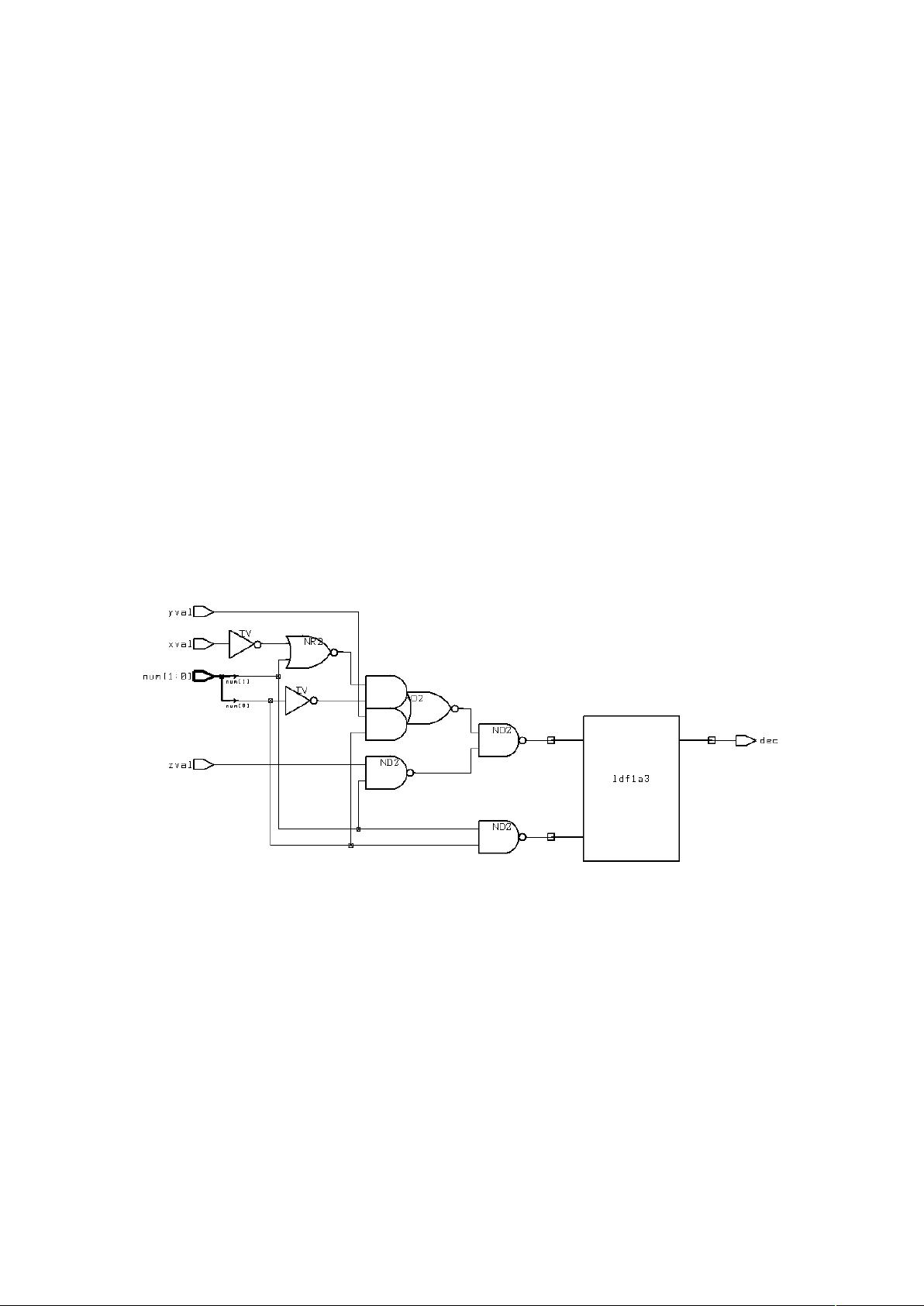

综合是集成电路设计流程中的关键步骤,其目标是将高层次的行为或RTL级描述转化为实际的、可制造的门级电路。Design Compiler通过转换、优化和映射三个阶段,将设计者的意图精确地转化为电路的物理实现。转换阶段,它将HDL代码转换为门级逻辑,利用gtech.db库中的门级单元构建电路。接着,优化阶段消除冗余,提升性能,并对不满足时序约束的部分进行调整。最后,映射阶段将优化后的电路映射到指定的工艺库,准备进行布局布线。

集成电路设计流程通常包括前端设计和后端实现,而综合恰好位于这两者之间,起到承上启下的作用。设计者需要在编写HDL代码时就考虑到可测试性,并在综合阶段设置合适的限制条件,这些条件通常源于系统级别的时序要求。一旦综合完成,生成的门级网表将用于后续的布局布线,直接影响到最终芯片的性能、面积和功耗。

综合的特点在于其限制条件驱动性,这意味着设计人员必须根据系统需求设定明确的约束,如最大时钟周期、面积限制等。这些条件不仅指导综合过程,也决定了设计的可行性和成功与否。同时,综合还要求设计者具备对工艺库的了解,以便选择最适合的逻辑元素进行电路实现。

在使用Design Compiler时,用户需要熟悉其命令行界面和脚本编写,以便有效地控制综合过程。此外,为了达到最佳效果,还需要对综合策略进行调优,包括逻辑等效替换、逻辑综合优化、时序约束管理和面积权衡等。

本资源提供了Design Compiler的详细介绍,涵盖了综合的基本原理、工作流程和特点,对于学习和使用这一工具的工程师而言,是一份宝贵的中文参考资料。通过深入学习和实践,设计者可以更好地驾驭Design Compiler,以实现高效、高质量的集成电路设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-07-11 上传

2018-05-08 上传

2021-10-04 上传

2012-05-22 上传

2021-04-16 上传

jessicayaoyi

- 粉丝: 0

- 资源: 1

最新资源

- node-selenium-driver-filedetector:具有文件检测器绑定的节点网络驱动程序

- spring-boot-graphql

- remixed2recipes

- 星级酒店预定主题响应式模板

- 企业门户网站管理系统,包括前台展示、后台管理、后端服务(Node.js、Koa、sequelize、MySQL),前.zip

- cordova-plugin-mmedia:千禧一代媒体广告的CordovaPhoneGap

- Lita:公司聊天室的机器人伴侣-开源

- eslint-plugin-jsx-extras:一组Eslint插件,用于基于应用程序的特定JSX规则

- bls_custom:粘在一起将Blocky Survival Minetest服务器固定在一起

- 进口玻璃磨边机PLC程序.rar

- Schizo-crx插件

- angular-starter:基于angularJS框架的全初始化前端项目

- javascript-dom-exercises-2.3

- TheGrid:按键游戏

- autotrader-scraper:用于刮擦自动交易器网站以获取汽车图像的工具。 我用它们来训练神经网络

- 库:通用功能的声明。 存储库的内容不属于GNU C库