基于Wishbone总线的UART IP核设计与应用

17 浏览量

更新于2024-09-01

收藏 221KB PDF 举报

本文主要探讨了在嵌入式系统和ARM技术中,如何设计一个基于Wishbone总线的UART IP核。随着嵌入式技术的广泛应用,UART(通用异步收发传输器)作为串行通信的关键组件,其IP核在片上系统中的集成变得越来越普遍。设计过程中,选择合适的片上总线是核心问题,而Wishbone总线因其开源和易实现的特性,成为一种经济高效的选择。

UART IP核设计原理:

1.1 UART工作原理:

UART负责将系统内部的并行数据转换为串行输出,同时处理从外部接收的串行数据。它不仅执行数据的串并转换,还添加奇偶校验位、启停标记,并进行错误检测。UART的正常工作依赖于一系列控制信号和数据信号,这些信号的处理直接影响到UART的设计。

1.2 Wishbone总线接口:

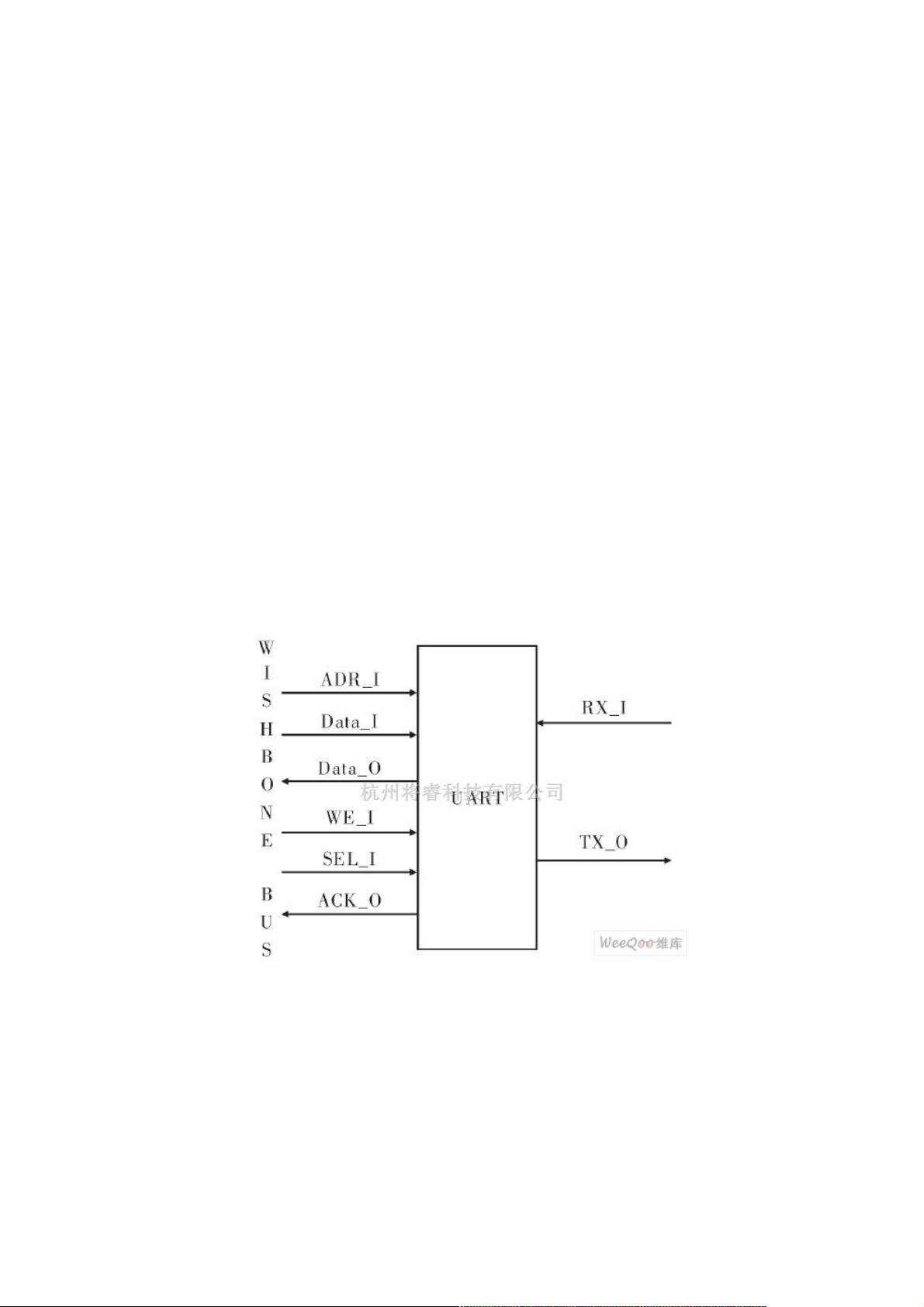

Wishbone总线是一种广泛使用的片上总线标准,提供了一种灵活且开放的架构,允许不同IP模块之间的通信。在UART IP核的设计中,采用Wishbone总线作为主机接口,可以简化与微处理器系统的连接。UART核通过Wishbone总线与其他系统组件交换控制信息和数据,其接口包含多个关键信号,如发送和接收数据线、控制信号线以及中断请求等。

UART IP核设计考虑因素:

- **成本效益**:使用基于Wishbone总线的UART IP核可以避免购买商业化UART IP核所需的授权费用,降低了设计成本。

- **性能**:Wishbone总线的灵活性使得UART IP核可以根据具体需求定制,从而优化性能。

- **可扩展性**:由于Wishbone总线的开放性和标准化,设计的UART IP核易于与其他遵循同样标准的IP核集成,增强了系统扩展性。

- **设计复杂性**:相较于专有总线,Wishbone总线具有更简单的规范,降低了设计和验证的复杂性。

设计流程:

设计基于Wishbone总线的UART IP核通常涉及以下步骤:

1. 总线接口定义:明确UART IP核与Wishbone总线交互的信号和协议。

2. 功能模块设计:实现UART的核心功能,如波特率发生器、数据缓冲区、奇偶校验计算等。

3. 总线适配器设计:将UART的功能模块与Wishbone总线接口连接,处理总线事务。

4. 时序分析和验证:确保UART IP核在不同的系统时钟条件下正确工作,并通过仿真验证其功能。

5. 封装和集成:将验证过的UART IP核封装成库,便于在目标平台上应用。

总结:

基于Wishbone总线的UART IP核设计是嵌入式系统和ARM技术中的一个重要实践,它结合了UART的串行通信功能和Wishbone总线的灵活性,为系统设计提供了经济、高效的解决方案。通过这样的设计,开发者能够快速地构建定制化的串行通信模块,满足特定应用的需求,同时降低了设计和维护的成本。

187 浏览量

153 浏览量

124 浏览量

112 浏览量

197 浏览量

111 浏览量

183 浏览量

234 浏览量

weixin_38714370

- 粉丝: 3

最新资源

- 使用Struts+Hibernate构建Web工程从零开始教程

- SQL基础操作与数据定义详解

- Win32 NetBIOS编程接口详解

- 数据库系统基础:习题解析与重点概念

- GNU Make中文手册:详解与指南

- Boost Graph Library用户指南与参考手册

- MAX471/MAX472高侧电流感知放大器在便携式PC和电话中的应用

- 51单片机AT89C51:入门与功能详解

- XML实用大全:探索XML在信息技术领域的应用

- 操作系统实验:处理机调度模拟

- B/S模式下的生产信息管理系统设计与实现

- TWIKI安装与配置指南

- OpenSceneGraph基础教程:3D场景图形解析

- 机器学习驱动的自动文本分类技术

- 数理逻辑入门:命题逻辑详解

- 理解OWL:构建语义网格的关键语言