DC时序约束深度解析:从概念到实践

"DC(design compiler)是一款强大的集成电路设计自动化工具,主要用于综合、时序分析和优化。本文将深入探讨DC中的时序概念,特别是setuptime和holdtime,以及相关的约束设置,适合初学者和进阶者学习。"

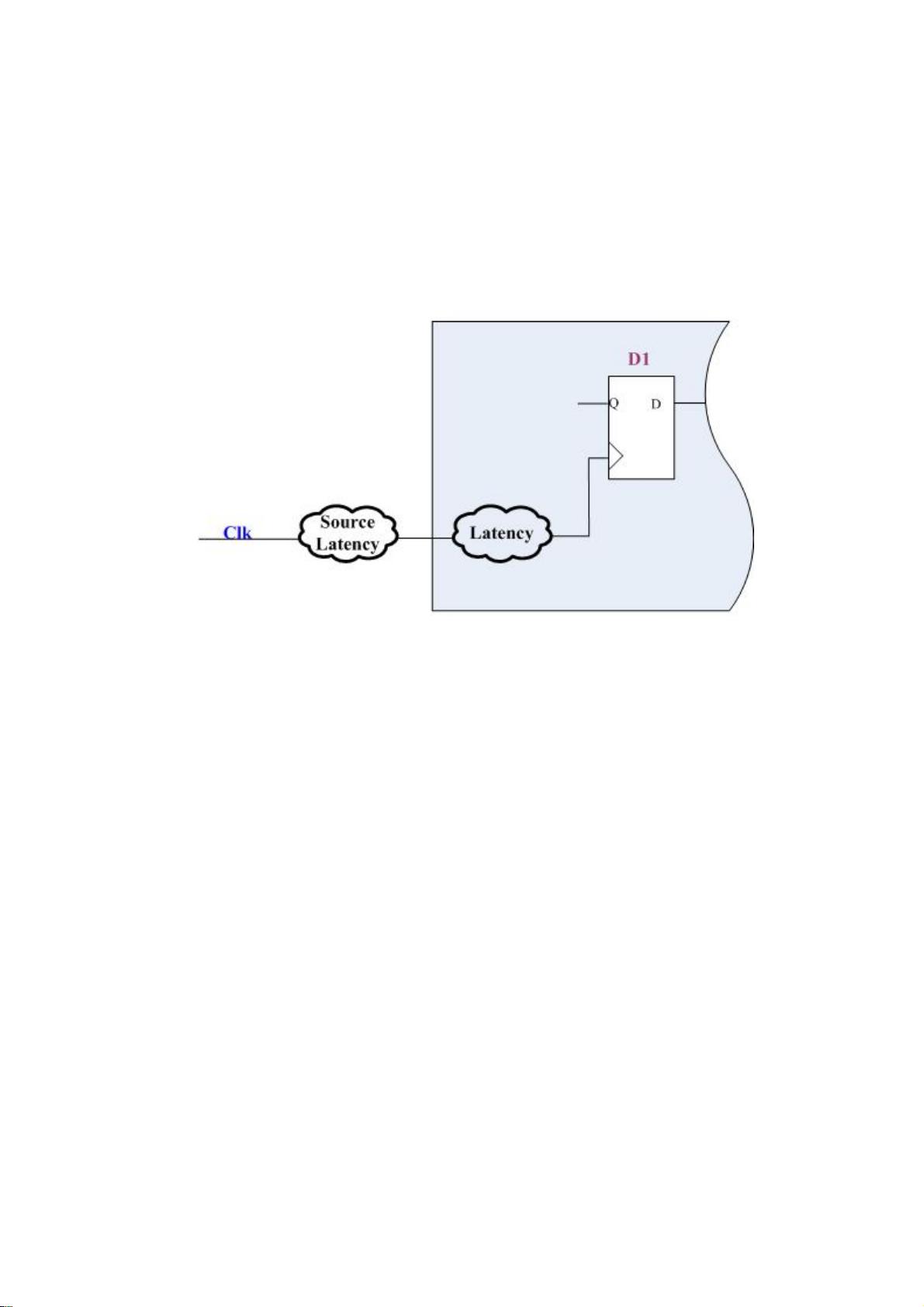

在集成电路设计中,时序约束是至关重要的,它们确保电路在规定的速度下正确运行。DC Design Compiler 提供了完善的时序约束机制,帮助设计者优化设计性能。setuptime和holdtime是时序约束的基础,它们定义了数据在时钟边沿前后必须稳定的时间。

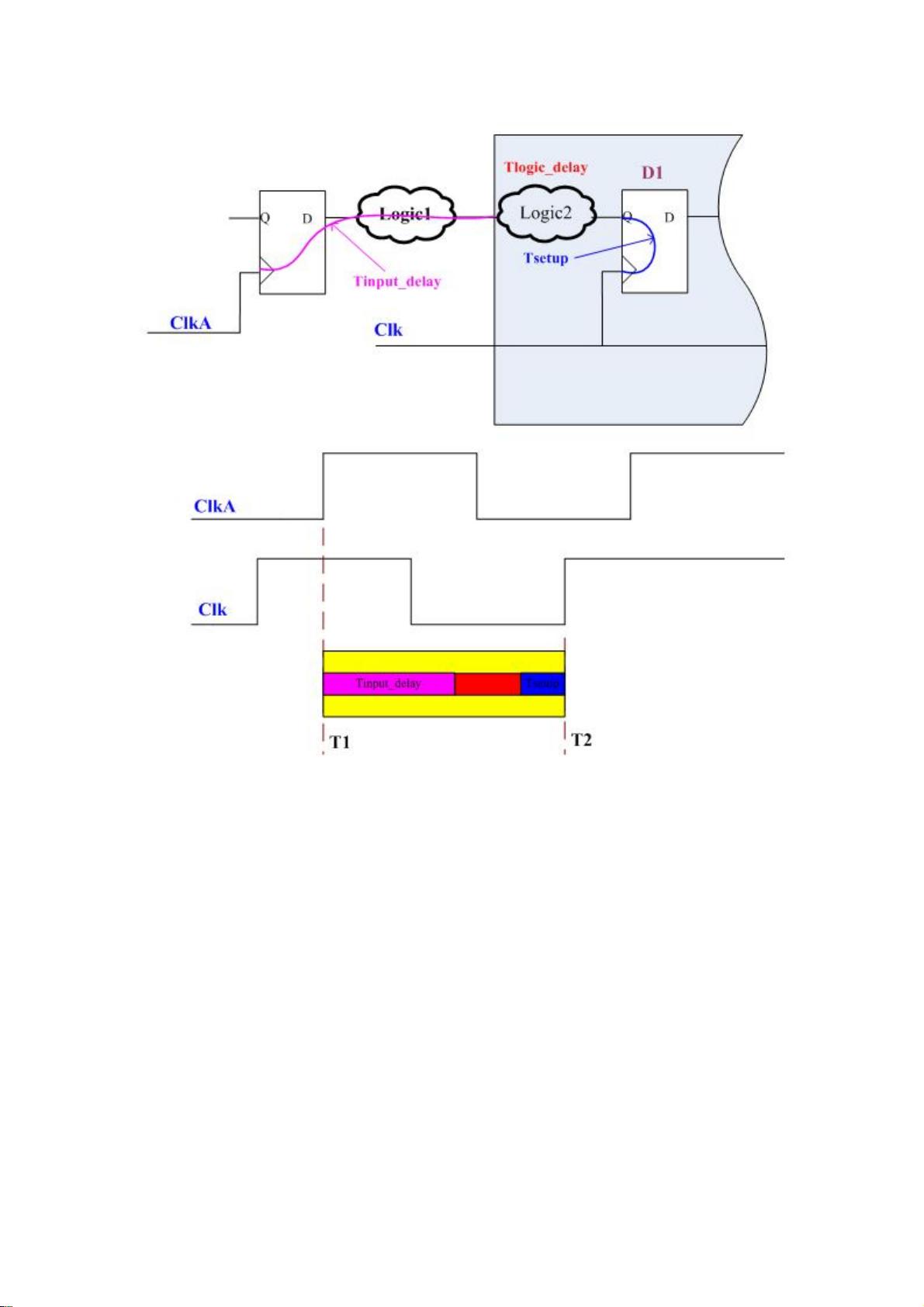

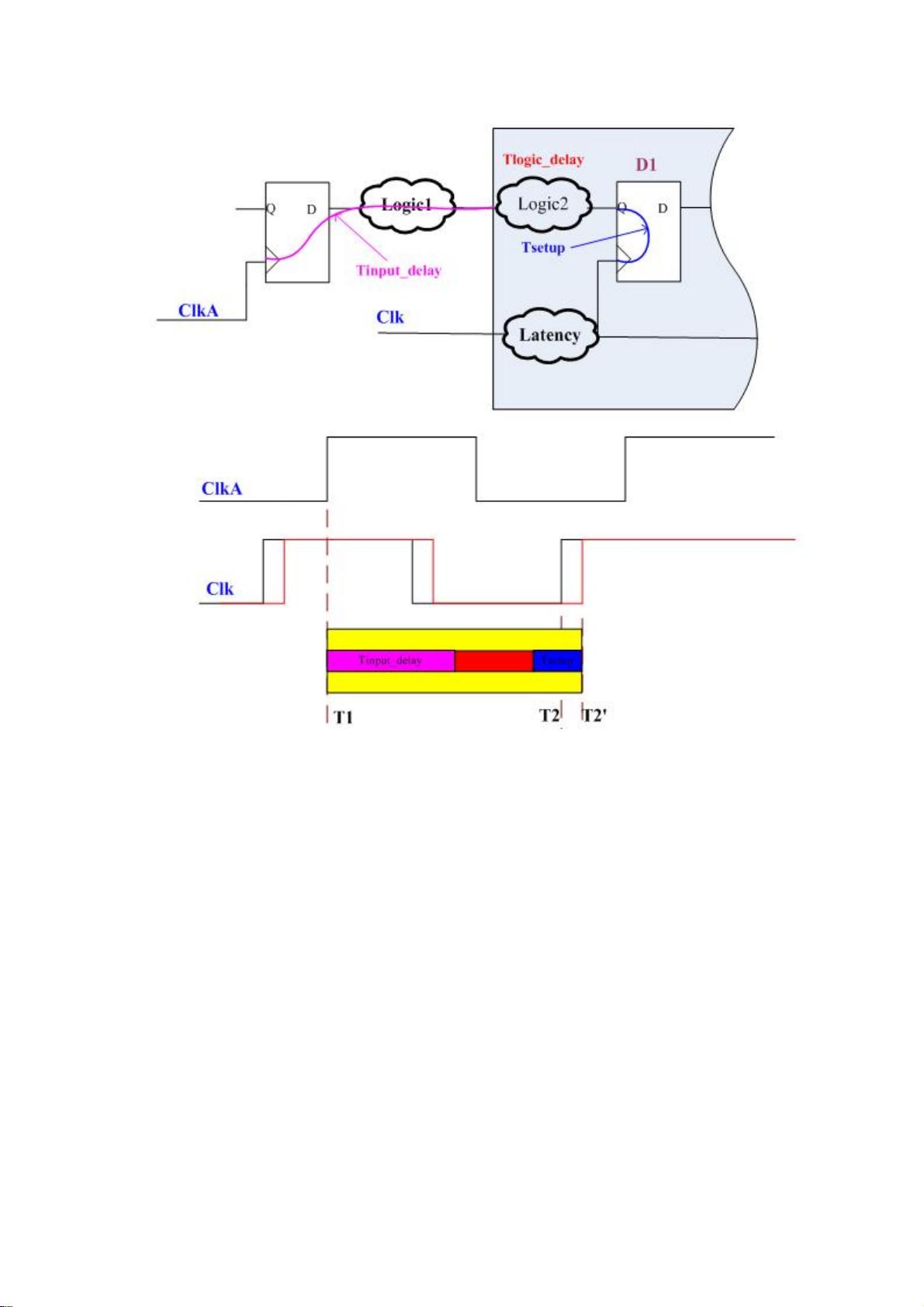

1. **Setuptime**:

建立时间是指数据信号必须在时钟信号上升沿到达之前稳定,确保触发器能够正确捕获输入数据。如果数据信号到达太晚,可能会导致错误的数据被存储,从而破坏电路功能。在DC中,时序分析会识别输入端口到触发器数据引脚(datapin)的路径,称为path1,来评估setuptime。

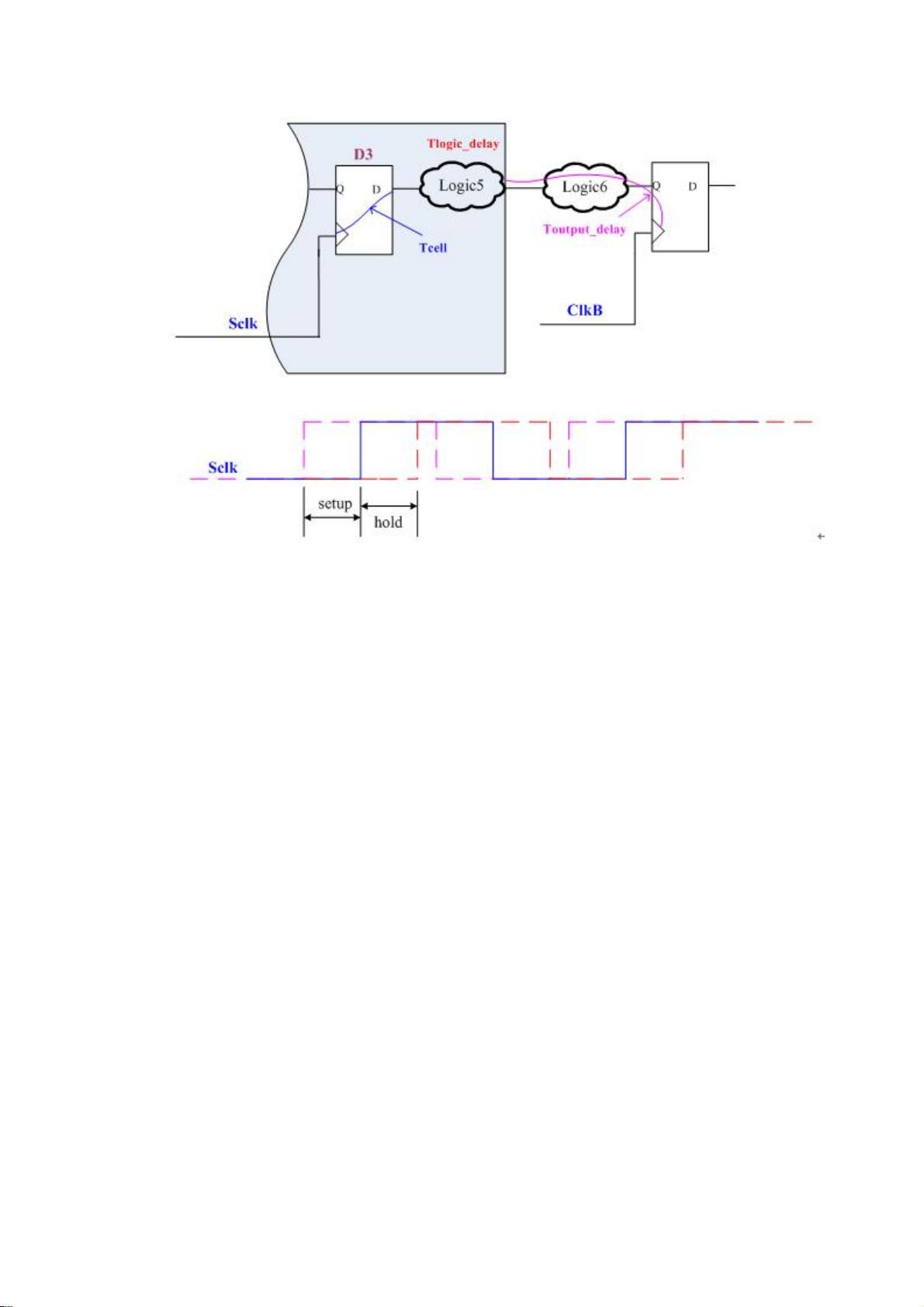

2. **Holdtime**:

保持时间是指时钟上升沿之后,数据信号必须保持稳定的时间,以防止时钟变化后数据发生漂移。如果数据在时钟边沿后变化,可能会导致触发器读取错误的数据。DC分析从触发器时钟引脚到下一个触发器数据引脚(path3)或输出端口(path4)的路径来检查holdtime。

3. **Fanout and Skew**:

扇出(fanout)是指单一逻辑门的输出连接到多个其他逻辑门的情况,可能导致信号延迟不一致,即扇出延迟。Skew是指同一时钟网络中不同位置的时钟信号到达时间差异,可能影响时序路径的正确性。在DC中,通过设置适当的约束,可以优化这些因素对时序的影响。

4. **Multicycle Path**:

多周期路径允许某些路径有较长的时序预算,这在某些设计中是必要的,例如,当处理大量数据流或在低功耗设计中减少时钟频率。DC提供了设置多周期路径的手段,以适应这些特殊需求。

5. **Gated Clocks**:

阀门时钟(gated clock)是指时钟信号经过额外逻辑门控制,这样的设计可以实现动态电源管理,但也会引入额外的时序复杂性。DC支持对这类时钟进行建模和约束,以确保时序的正确性。

6. **Input/Output Constraints**:

输入和输出约束涉及到芯片与外部世界的接口。这些约束包括驱动能力、摆率限制、输入延迟和输出负载等,确保IO接口与系统其余部分同步并满足电气规范。

7. **Optimization Constraints**:

优化约束则指导DC如何进行逻辑和物理优化,例如最小化面积、功耗或速度。用户可以通过指定目标速度、面积限制或其他参数来控制优化过程。

理解并正确设置这些约束对于确保集成电路设计的成功至关重要。DC Design Compiler提供了丰富的工具和功能,帮助设计者在复杂的IC设计流程中实现高效的时序管理和优化。通过深入学习和实践,设计者可以更好地掌握DC的使用,提升设计质量和效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-07-14 上传

2010-06-05 上传

2022-07-13 上传

139 浏览量

2023-06-02 上传

点击了解资源详情

c826915496

- 粉丝: 0

- 资源: 1

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程