2018汇顶IC笔试: PLL电路与时序路径分析

需积分: 50 49 浏览量

更新于2024-07-18

10

收藏 896KB PDF 举报

"该资源是2018年汇顶科技公司针对数字IC前端和后端岗位的笔试题目,包含了编程题目以及与集成电路设计相关的理论问题。主要关注PLL(锁相环)电路和时序路径分析两个核心知识点。"

PLL(锁相环)电路是数字集成电路中的关键组件,其主要功能是将输入的参考时钟调整到所需的频率。在 PLL 中,正确答案是 B 和 D。B 项指出 PLL 可以输出分频、倍频、分数频的时钟,这是 PLL 的基本功能,能够根据应用需求灵活调整输出频率。D 项提到 PLL 的 jitter 值并不等于同步数字电路中的 clock uncertainty 设定值,这反映了 PLL 在处理时钟抖动(jitter)上的复杂性,jitter 在PLL 输出时可能会被改善或恶化,取决于PLL的设计和性能。

PLL电路的工作原理是通过比较输入参考时钟与VCO(压控振荡器)产生的时钟之间的相位差,然后调整VCO频率来使两者保持同步。这个过程可以通过鉴相器、低通滤波器和VCO等组件来实现。PLL 电路不仅可以用于频率合成,还广泛应用于时钟恢复、数据通信等领域。

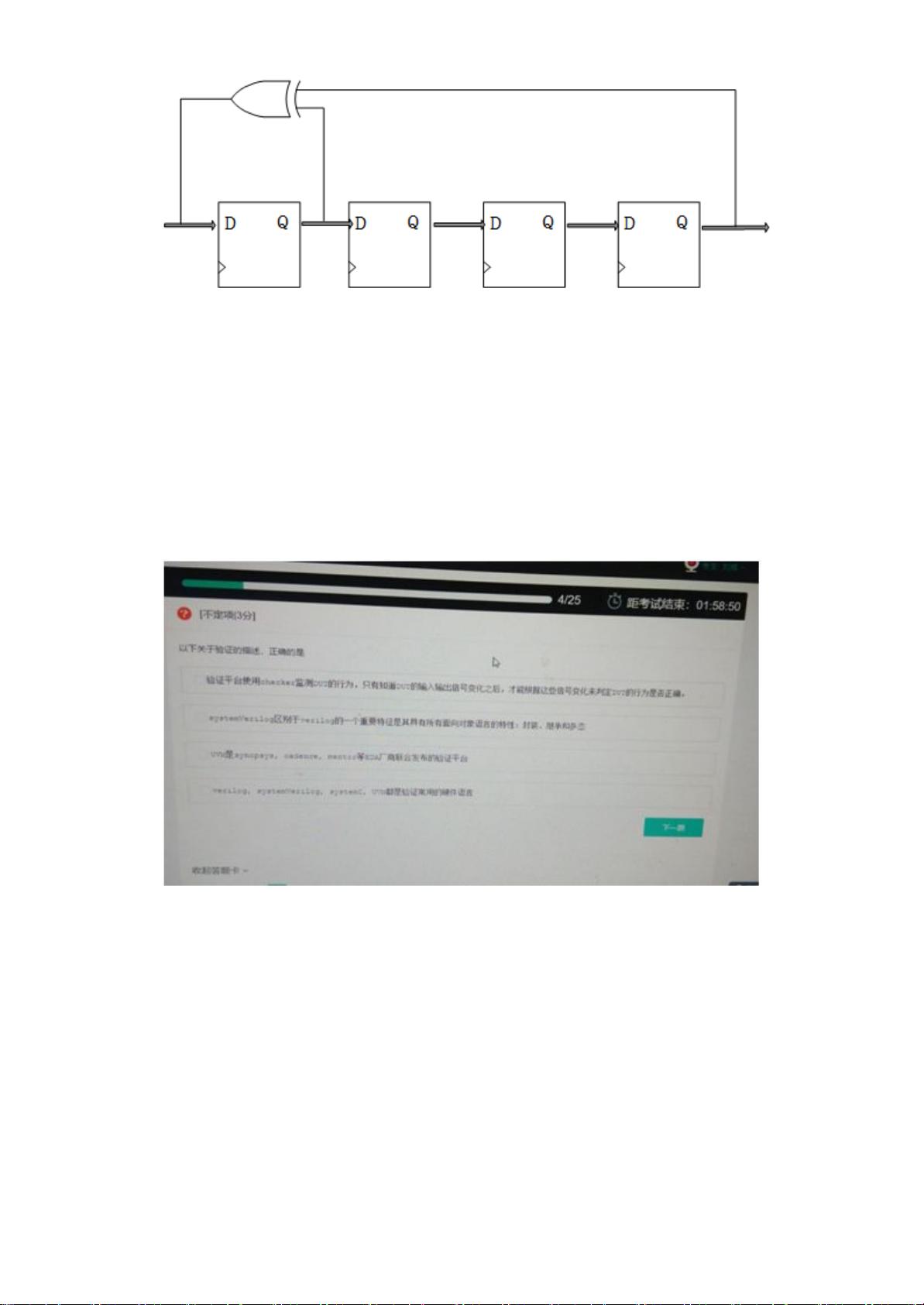

另一方面,时序路径分析是数字集成电路设计中的重要环节,用于确保电路在给定的时间内正确无误地工作。题目中的第二部分涉及了如何约束和优化这些路径。正确的描述是 D 项。在给定的时序路径示意图中,每个时序路径都由组合逻辑和寄存器(FF1/FF2)组成,约束这些路径的延时对于保证电路的时序合规至关重要。

1. A 到 FF1 的路径需要满足输入信号到达FF1之前,寄存器的建立时间要求(Tsetup)得以满足,因此需要提供Tclk和输入延迟(Tin_delay)信息。

2. FF1 到 FF2 的路径,需要考虑CLK到D端的传输延时,同时考虑寄存器的输出延时(Tcq)和建立时间要求。

3. FF2 到 Z 的路径,需要考虑输出端口的延迟(To_delay)以及后续寄存器的建立时间。

4. A 直接到 Z 的路径,涉及到整个组合逻辑F的延时,需要所有相关延时参数以满足时序约束。

进行时序分析时,EDA(电子设计自动化)工具通常需要输入时钟周期(Tclk)、输入/输出延迟、寄存器延时等信息,以便计算并约束组合逻辑的延迟,保证整个系统的时序正确性。对于设计者来说,理解这些概念并能正确设置约束是至关重要的,因为这直接影响到集成电路的性能和可靠性。

265 浏览量

196 浏览量

131 浏览量

3188 浏览量

630 浏览量

688 浏览量

296 浏览量

2022-09-21 上传

Desmond_0225

- 粉丝: 2

- 资源: 4

最新资源

- SMTPSender(iPhone源代码)

- 类似瀑布流的网格视图效果

- win7 64位安装IE11所需补丁

- WIFIRobots

- 多路DA上位机+单片机源码.zip

- cace:CMS管理员命令执行

- cursoKuberneteswildfly:Curso cursoKubernetes野蝇sobre Cubernetes

- mysql-connector-java-8.0.25.zip

- 建筑节能平台登录网页模板

- 网络游戏-基于移动无线网络、通过远程服务器进行地图解析的方法.zip

- PCBMill:PCBMill FABtotum插件

- 房屋出租管理系统.rar

- Google Chrome:trade_mark:的标签管理器-crx插件

- WindowsFormsApp1.zip

- agora:面向目标的敏捷需求获取

- webtesting-ii-guided:Web测试II模块指导项目