Verilog HDL基础教程:快速入门

需积分: 50 72 浏览量

更新于2024-07-26

收藏 269KB PDF 举报

"这是一份详细的Verilog HDL入门教程,涵盖了从基础知识到高级概念的多个方面,旨在帮助初学者理解和掌握这种广泛用于 ASIC 设计的硬件描述语言。教程介绍了Verilog HDL 的基本语法、建模方法以及各种操作符和表达式的用法。"

在Verilog HDL中,学习者首先会接触到的是语言的基础部分,包括标识符(4.1节),这是编程中的基础元素,用于命名变量、模块等。接着是注释(4.2节),它是理解代码的关键,尤其是在复杂的项目中。4.3节讨论了格式规范,确保代码的可读性。此外,4.4节介绍了数字值集合和常量,这些都是编写Verilog代码时定义和操作数据的基本要素。

数据类型的定义在4.5节,包括线网类型(4.5.1)和寄存器类型(4.5.2),这些是硬件设计中常见的两种主要数据载体。4.6节详细阐述了运算符和表达式,包括算术运算符(4.6.1)、逻辑运算符(4.6.3)、按位逻辑运算符(4.6.4)、条件运算符(4.6.5)、连接运算符(4.6.6)以及条件语句(4.7节)和case语句(4.8节),这些都是控制程序流程和进行逻辑操作的关键。

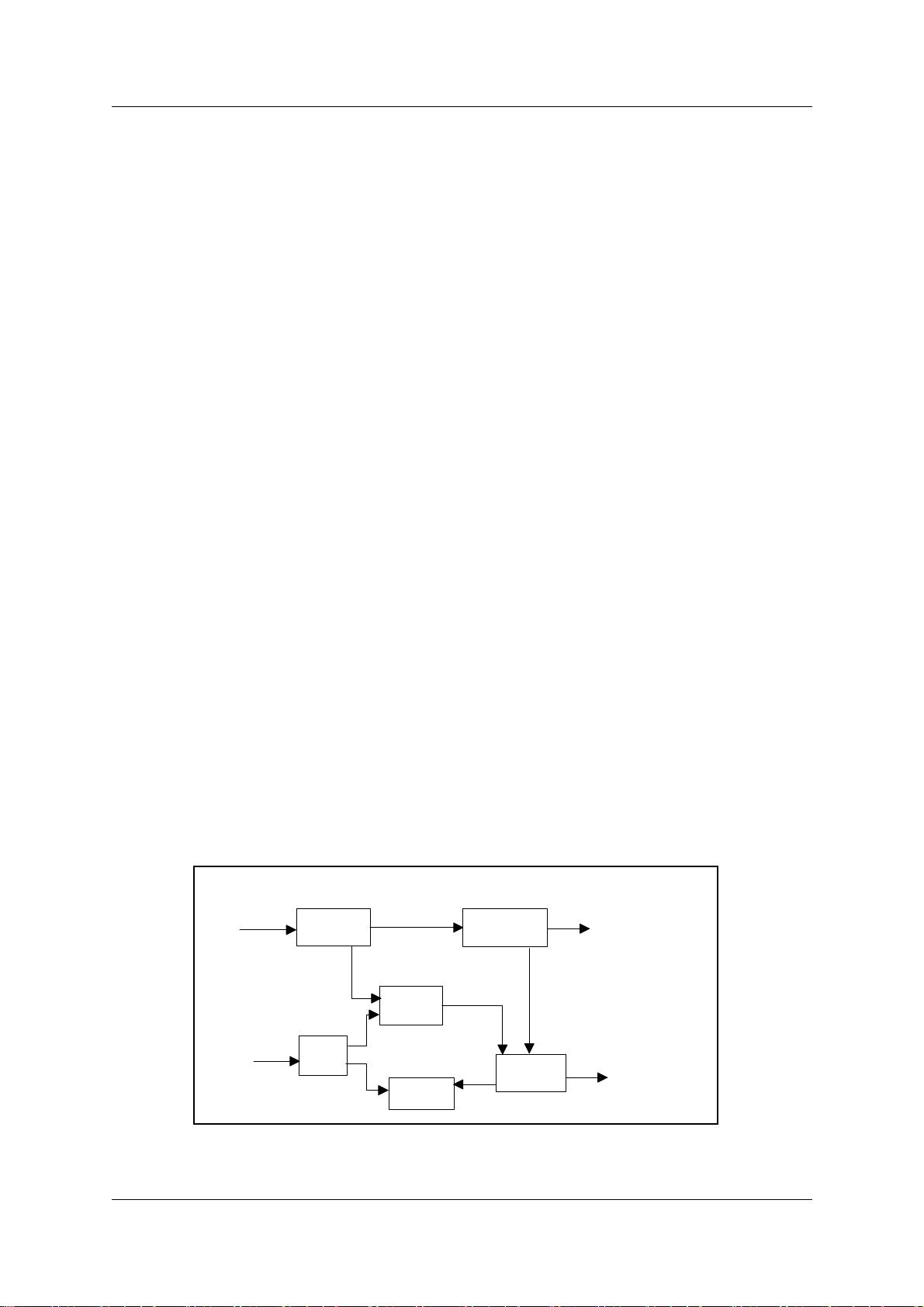

教程进一步深入到Verilog的建模方式,3.1至3.3节详细讲解了Verilog的建模概述,包括结构化描述(3.3.1)、数据流描述(3.3.2)、行为描述(3.3.3)以及混合设计描述(3.3.4)。这些建模方式是描述硬件系统结构和行为的基础。

模块是Verilog的核心,从3.1节开始介绍,包括模块的结构(3.1.2)、模块语法(3.1.3)以及简单的实例。模块用于构建复杂的硬件结构,可以包含输入、输出和内部元件。

7.1至7.4节讲解了行为建模,这是描述硬件行为的重要部分,包括过程赋值语句(7.2节)、顺序语句块(7.3节)和行为建模的具体实例(7.4节)。这部分内容让设计者能够描述硬件的行为逻辑。

6.3节则涉及数据流建模的具体实例,这是描述数据如何在硬件系统中流动的方式。此外,教程还涵盖了其他方面(8节),如习题(9节)和保留字(10节),以帮助巩固学习者的知识并扩展其对Verilog的理解。

这份Verilog HDL入门教程详尽地介绍了语言的基本元素、建模方法和实际应用,对于想要进入数字电路设计领域的学习者来说,是一份非常宝贵的资料。通过学习这份教程,读者将能够熟练地使用Verilog HDL来描述和实现数字系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

117 浏览量

2010-04-03 上传

249 浏览量

168 浏览量

点击了解资源详情

根号3

- 粉丝: 1

- 资源: 6

最新资源

- python代码自动办公 Excel_更灵活的操作方式 项目源码有详细注解,适合新手一看就懂.rar

- 基于基于粒子滤波器的SLAM算法实现地图的成像matlab仿真

- 《鬼鬼盯着你》绘本故事PPT模板

- alfabetizar.aprender.digital

- 紫色花朵 潮流壁纸 高清风景 新标签页 主题-crx插件

- hveto_graph:hveto 摘要页面的 D3.js 版本

- who-does-not-follow-me:一个Node.js脚本,用于检查谁没有在GitHub上关注您

- CSS3地图热点文字标注提示特效代码

- python代码自动办公excel处理实例(单工作簿拆分到多工作簿中(多表中) 项目源码有详细注解,适合新手一看就懂.rar

- 对tabcontrol的应用及tabpage的处理

- emv:EMV芯片和PIN库

- giffus:一个允许用户通过互联网发送礼物的小型社交应用程序。 支持音乐等多种类型的礼物,特别是打开礼物,接收者必须去发送者想要的地方

- github-repos-react:添加GitHub repos并查看其详细信息和问题

- Khayyam-crx插件

- smoothing(imagetosm_ooth)_滤波_去噪_通信去噪_

- 局域网 【飞秋】 【FeiQ】 下载