FPGA Quartus 2流水线乘法累加器宏功能模块详解

需积分: 46 4 浏览量

更新于2024-07-25

1

收藏 1.56MB PPT 举报

本篇文章主要探讨了在FPGA Quartus II工具中应用宏功能模块进行流水线乘法累加器的设计。首先,文章介绍了EDA(电子设计自动化)技术,这是一种广泛用于硬件设计的关键技术,它简化了复杂的数字电路设计过程。

在第4章的详细内容中,作者着重讲解了流水线乘法累加器的设计方法。这个设计过程包括以下几个关键步骤:

1. 电路结构与工作原理:设计者首先构建了一个基础的电路结构,如图3-1所示的流水线乘法累加器顶层设计,该设计利用了LPM(逻辑综合器中的预置模块)来提高性能。LPM提供了预先优化过的IP核,如乘法器和加法器。

2. 调用乘法器与参数设置:在设计中,通过调用LPM乘法器并设置其参数,如图3-4和图3-5所示,可以调整乘法器的结构类型和工作方式,使其适应流水线的需求。

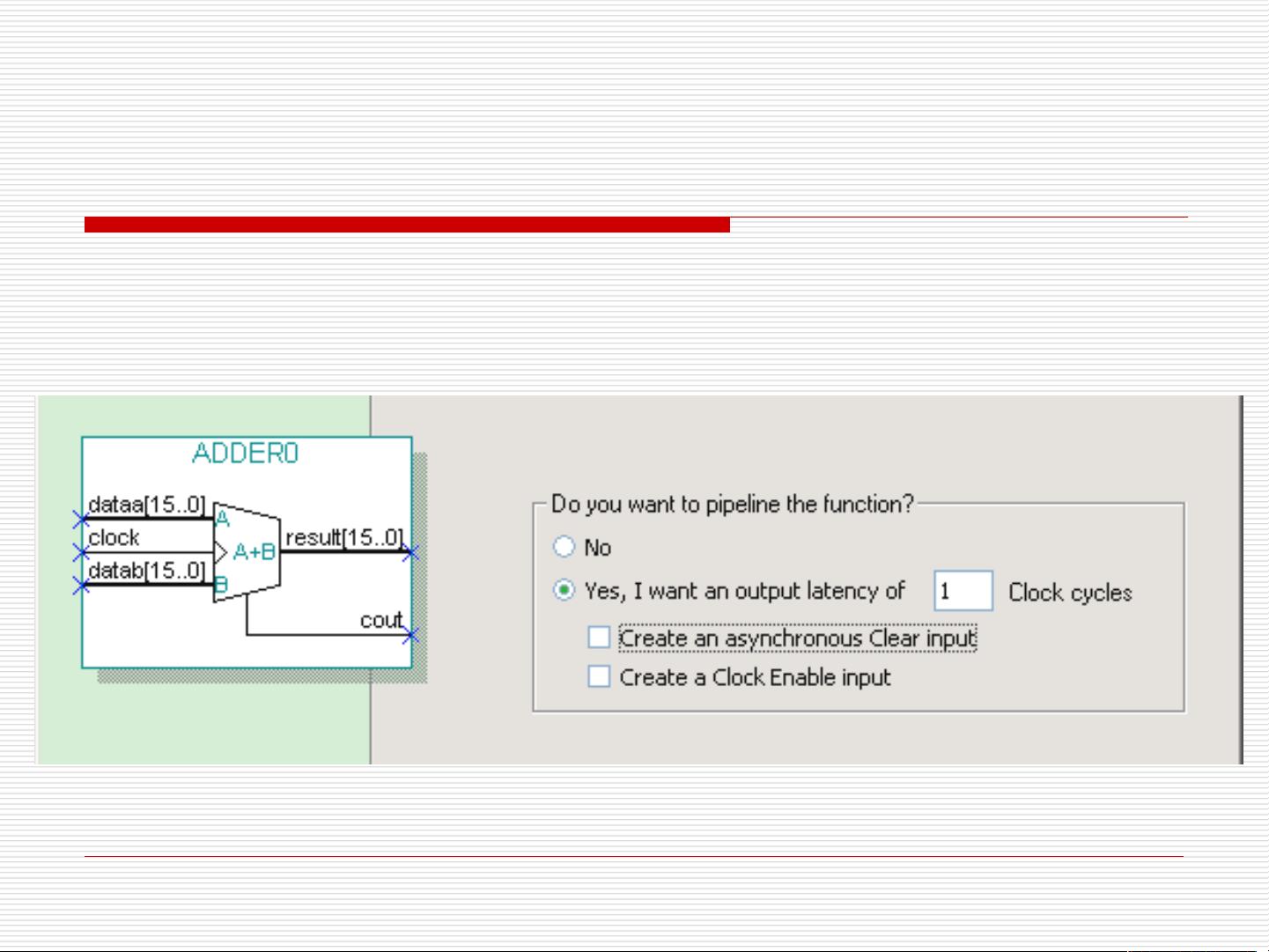

3. 流水线配置:接着,设计者设置了加法器的数据输入类型和流水线功能,例如选择特定类型的加法器和设置进位输出(图3-8至图3-10),以实现高效的并行计算。

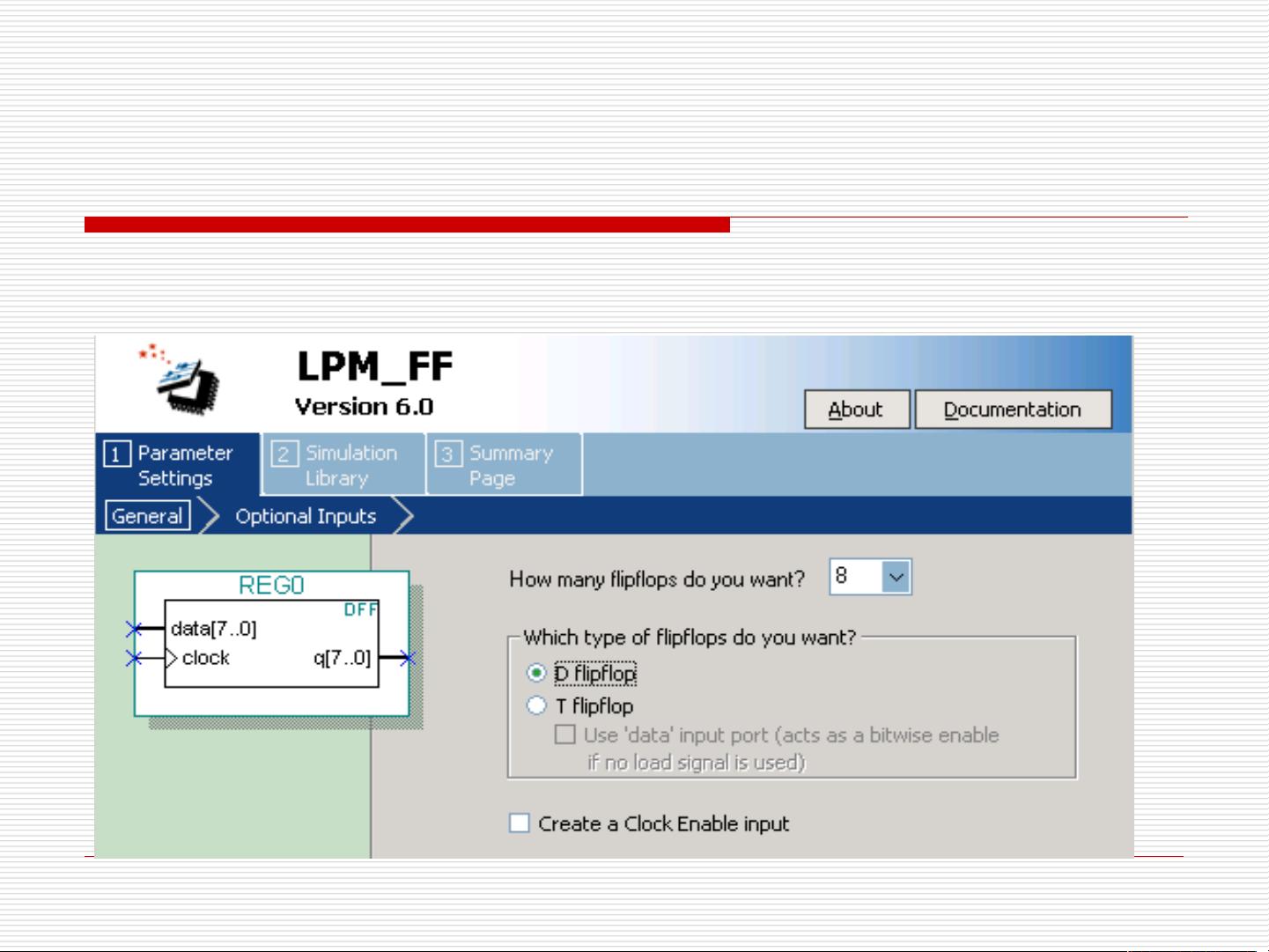

4. LPM寄存器选择:使用D触发器类型对LPM寄存器进行配置,如图3-11所示,以确保数据的正确存储和传递。

5. 电路时序仿真与测试:设计完成后,进行了电路时序仿真,如图3-12至图3-15所示,以验证设计的正确性和性能。这部分涉及到基于逻辑宏单元和专用嵌入式乘法器模块的两种不同设计方案的比较分析。

通过这些步骤,读者可以了解到如何利用FPGA Quartus II的宏功能模块来高效地设计和实现流水线乘法累加器,这在处理大规模、高精度的数值运算时具有显著的优势。这种设计方法对于理解和实践FPGA编程以及硬件加速算法有很高的实用价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-14 上传

2022-09-24 上传

2020-06-22 上传

2021-05-20 上传

2022-08-08 上传

2012-09-25 上传

小晓样

- 粉丝: 1

- 资源: 6

最新资源

- Web_Service开发指南_2.3.1

- wordpress 主题教程

- 网上商店论文大学生博客

- Think In perl

- JSTL帮助文档(使用说明)

- Web_Service开发指南_2[1].3.1.pdf

- Flex(3.0)体系架构剖析

- JavaScript web转word文档

- I2C总线应用中的几个问题

- 基于Java的搜索引擎

- EXT学习,EXT电子书

- 计算机系统--程序员视角,computer system- a programmer's perspective

- 跟我学习DLL(入门必备)

- EXT学习,EXT电子书

- SQL操作全集,整理后的文档

- 英语新概念详细分析....................................