探索组合逻辑电路:门电路验证与全加器设计

需积分: 0 72 浏览量

更新于2024-06-30

收藏 3.14MB DOCX 举报

本次实验名为"第一次实验_周玉川_20172213020061",由电子科技大学信息与软件工程学院的学生周玉川在2018年6月9日完成,是在数字逻辑课程的学习背景下进行的。实验的主要目标包括理解常用集成门电路的功能与特性,熟悉逻辑符号,掌握集成电路的外引线排列和使用方法,以及学习组合逻辑电路的分析、设计和测试。

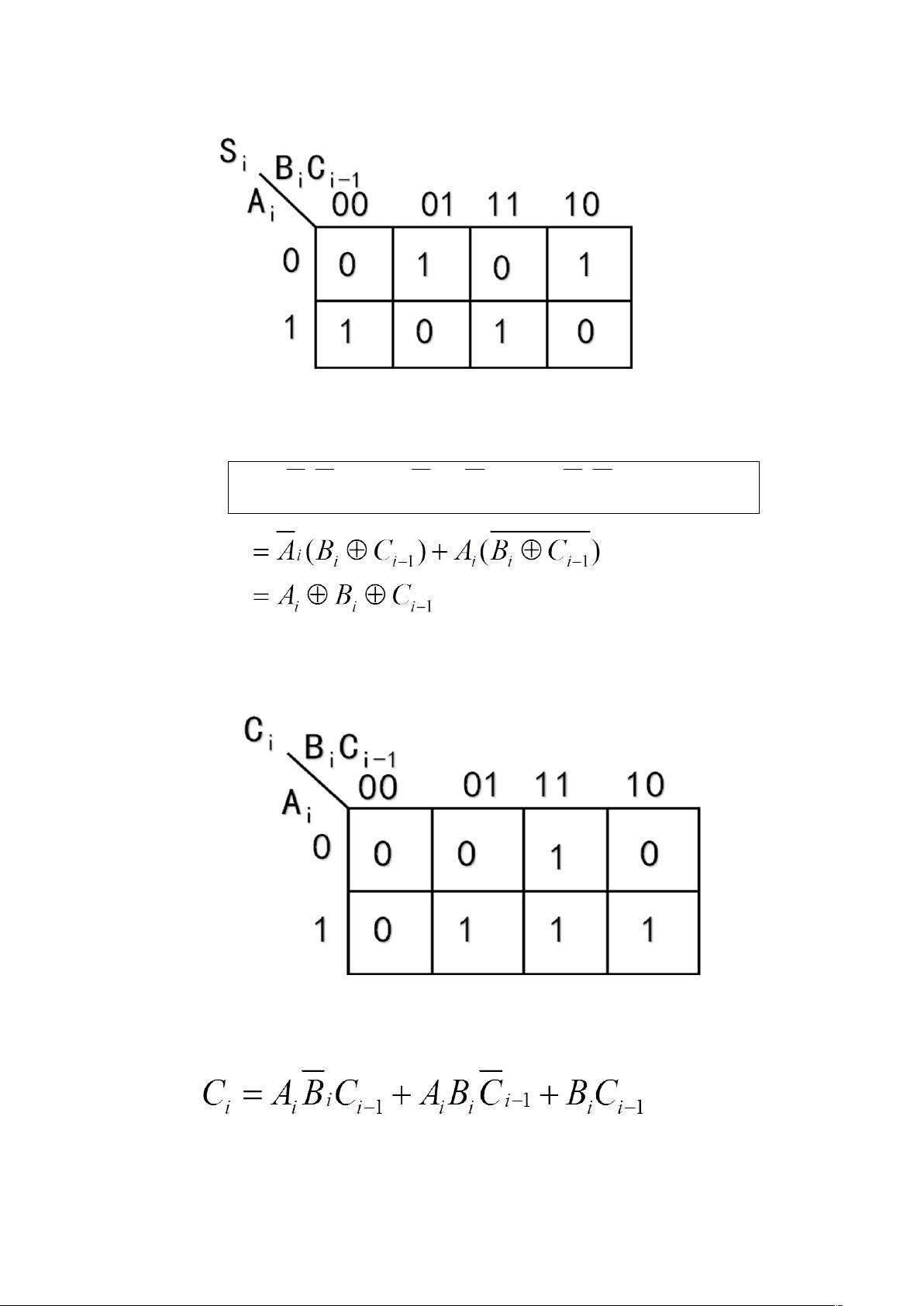

实验的核心内容分为两部分:一是组合逻辑电路的分析方法,涉及逻辑抽象,即理解事件之间的因果关系,识别输入变量和输出变量;逻辑赋值,定义逻辑状态的含义,通过"0"和"1"表示不同状态;构建真值表来描述逻辑关系;并进一步化简逻辑函数表达式,最后绘制逻辑电路图。二是全加器或全减器的设计实践,利用74LS86异或门和74LS00与非门构建这种电路,通过真值表驱动,观察输出结果和进位/借位信号,记录数据以便分析。

实验所需的设备和材料有数字逻辑试验箱、导线、集成器件如74LS00、74LS04和74LS86。实验步骤具体到实际操作,如插入逻辑门电路,调整输入和输出,以及用电路图的形式展示设计过程。

实验结果显示,对于部分TTL门电路,特别是异或门,进行了逻辑功能的验证,通过实际操作和数据记录,验证了电路的预期行为。这部分实验有助于深入理解门电路的工作原理和实际应用。

在整个实验过程中,学生不仅锻炼了逻辑分析和设计技能,还学会了如何将理论知识应用于实际电路设计,以及如何通过实验结果进行数据分析,这些都是数字逻辑课程的重要组成部分。通过这样的实践,学生能够提升对数字逻辑电路的理论掌握和实践操作能力,为后续的科研和工程工作打下坚实基础。

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

AshleyK

- 粉丝: 26

- 资源: 315

最新资源

- 行业数据-20年9月份中国城市商铺房价对比.rar

- permission:一款带ui基于RBAC模型的可自由配置的原生的权限框架

- c-vector:C中的动态数组实现。类似于标准C ++中的Vector

- music_vue:基于网易云的音乐播放app

- Office_break:Proyecto de DEV和IPV。 正式销售:)

- tf-dr:TinyFugue 和 DragonRealms

- travel

- byte-buddy-agent-1.11.22-API文档-中文版.zip

- Academic_Department:苏州大学计科院院研会学术部

- seasons

- force-rest-api:用于Force.com REST API的Java库

- codealong_angular

- donmik-shootemup-quintus:这是用 Quintus.js 编写的射击游戏

- Face-Mask-Detection-Using-CNN

- SimpleEngine

- Picture-Perfect:创建视觉评估报告的工具