理解FPGA中的OSERDESE2:并行-串行转换技术

需积分: 50 29 浏览量

更新于2024-09-08

2

收藏 272KB DOCX 举报

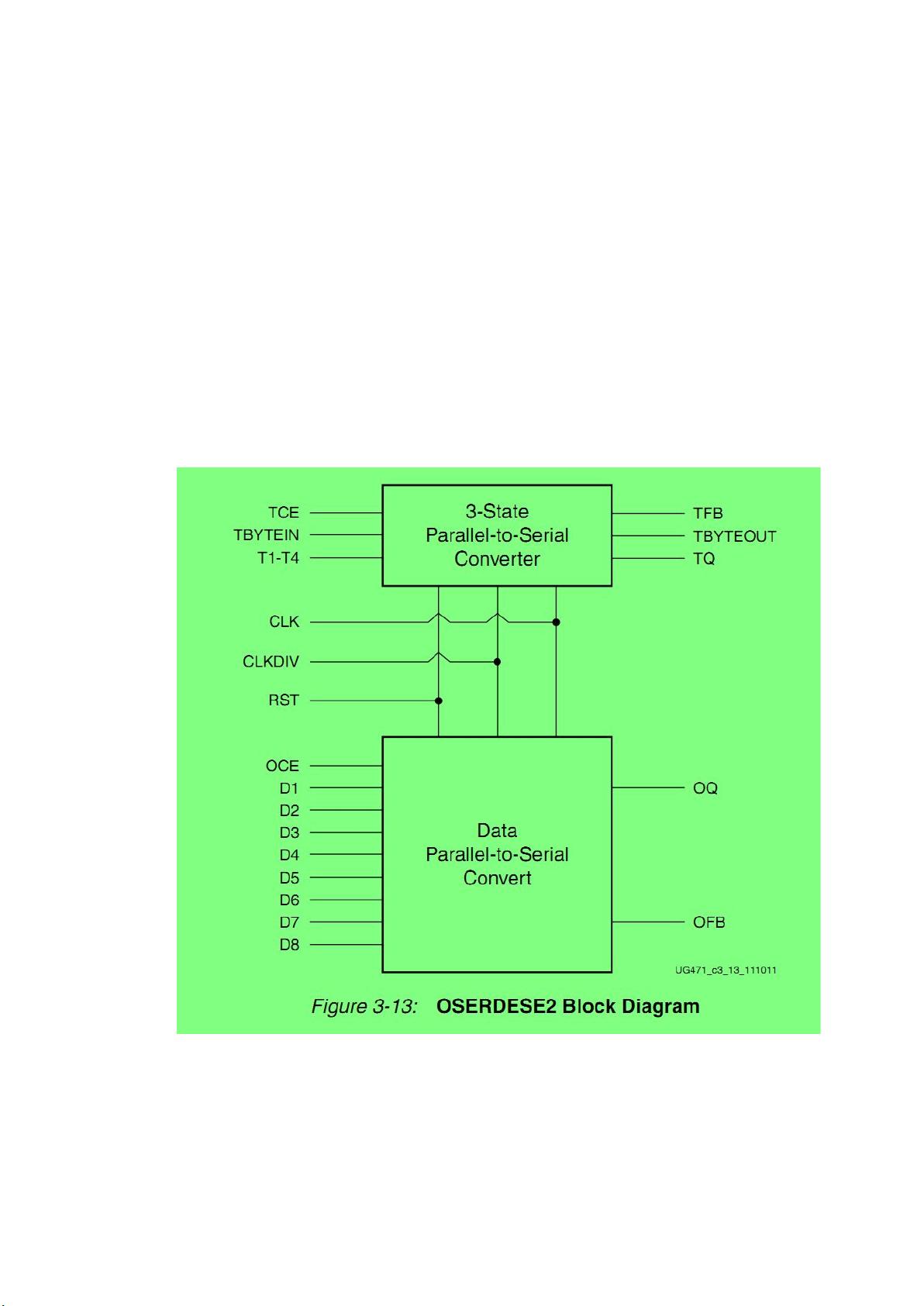

"OSERDESE2是Xilinx 7系列FPGA中的一种专用并行-串行转换器,主要用于实现高速源同步接口。它包含了数据和三态控制的独立串行器,支持SDR和DDR模式,适用于高速内存应用。每个OSERDESE2模块能处理2至8位(或14位,使用宽度扩展)并行数据,通过OQ输出端口以串行形式传输。在DDR模式下,数据速率可翻倍。"

OSERDESE2的核心功能在于其数据并行到串行转换器,该转换器接受并行数据,将其序列化后通过OQ引脚输出。数据的序列化顺序是从最低位开始向最高位传递。OSERDESE2的操作依赖于两个时钟信号:CLK是高速串行时钟,CLKDIV是分频并行时钟,两者必须保持相位对齐。在使用OSERDESE2前,需对其施加复位,确保内部计数器的正确初始化。否则,非同步复位的撤销可能导致输出异常。

此外,OSERDESE2还包括一个三态控制的并行到串行转换器,用于IOB的三态控制信号。但与数据转换不同,三态转换器仅能串行化4位并行3态信号,且不可级联。数据路径的输出通过OQ端口进行,但OQ不能直接驱动ODELAYE2,OFB引脚应用于此目的。OFB端口还可以将串行数据反馈给ISERDESE2,或者连接到ODELAYE2原语。

三态控制方面,OSERDESE2提供了两个输出端口:TQ和TFB。TQ端口将三态并行-串行转换器的输出连接到IOB的控制/3态输入,而TFB端口则提供给用户,用于向结构发送OSERDESE2的3态控制信号,这在某些设计中可能是必要的。

在实际项目中,理解和有效利用OSERDESE2的这些特性至关重要,尤其是对于需要高速、低延迟通信的场合。通过适当的时钟管理、复位控制和数据路径配置,可以优化OSERDESE2在系统中的性能,确保源同步接口的稳定性和可靠性。学习和掌握OSERDESE2的使用技巧,对于提升FPGA设计能力具有积极意义。

点击了解资源详情

点击了解资源详情

103 浏览量

105 浏览量

358 浏览量

448 浏览量

145 浏览量

458 浏览量

2022-12-18 上传

酱油地

- 粉丝: 1

- 资源: 29

最新资源

- 一个帮助实现条形码扫描的库-Android开发

- casile:CaSILE工具包,采用SILE和其他向导的图书出版工作流程

- TextureSwiftSupport:一个使我们获得DSL来在Texture中定义布局规范的库[如SwiftUI]

- 高端大气星级酒店展示网站静态模板.zip

- PING-开源

- 雷达成像中的时频分析成像

- WebRtcAecmSample:这是一个aecm示例(使用webrtc)

- bluetooth.rar_android 蓝牙_android bluetooth_android蓝牙_蓝牙_蓝牙通信

- area_of_a_regular_polygon

- LibraryPractice_20210327

- ruby-on-rails-cassandra:Ruby on Rails与Cassandra

- 泛型MakeGeneric方法应用实例.rar

- 影刀RPA系列公开课3:网页自动化——数据抓取.rar

- formation_control-master.zip_formation control_formation_control

- matlab标注字体代码-MATLAB-Tools:为MATLAB生成的一组脚本,这些脚本可能在您自己的项目和文件中有用

- flex-masonry:用CodeSandbox创建