门控时钟技术在低功耗时序电路设计中的应用

119 浏览量

更新于2024-09-02

收藏 293KB PDF 举报

"本文主要探讨了在电源技术中如何利用基于门控时钟的低功耗设计策略,特别是在时序电路领域。文章以约翰逊计数器为例,展示了如何通过有效的门控时钟来实现高能效的时序电路设计,以适应移动设备对低功耗的需求。"

在当前的电子设计领域,电源效率已经成为关键考虑因素,特别是在移动设备中,电池寿命直接影响用户体验。传统的设计方法中,所有计算和数据处理都依赖于全局时钟信号,这不仅增加了时序电路的数量,还带来了较高的功耗。为了解决这个问题,设计师们开始采用电源域划分和门控时钟技术,能够在不需要运行某些电路时关闭或降低其工作电压,从而显著减少整体功耗。

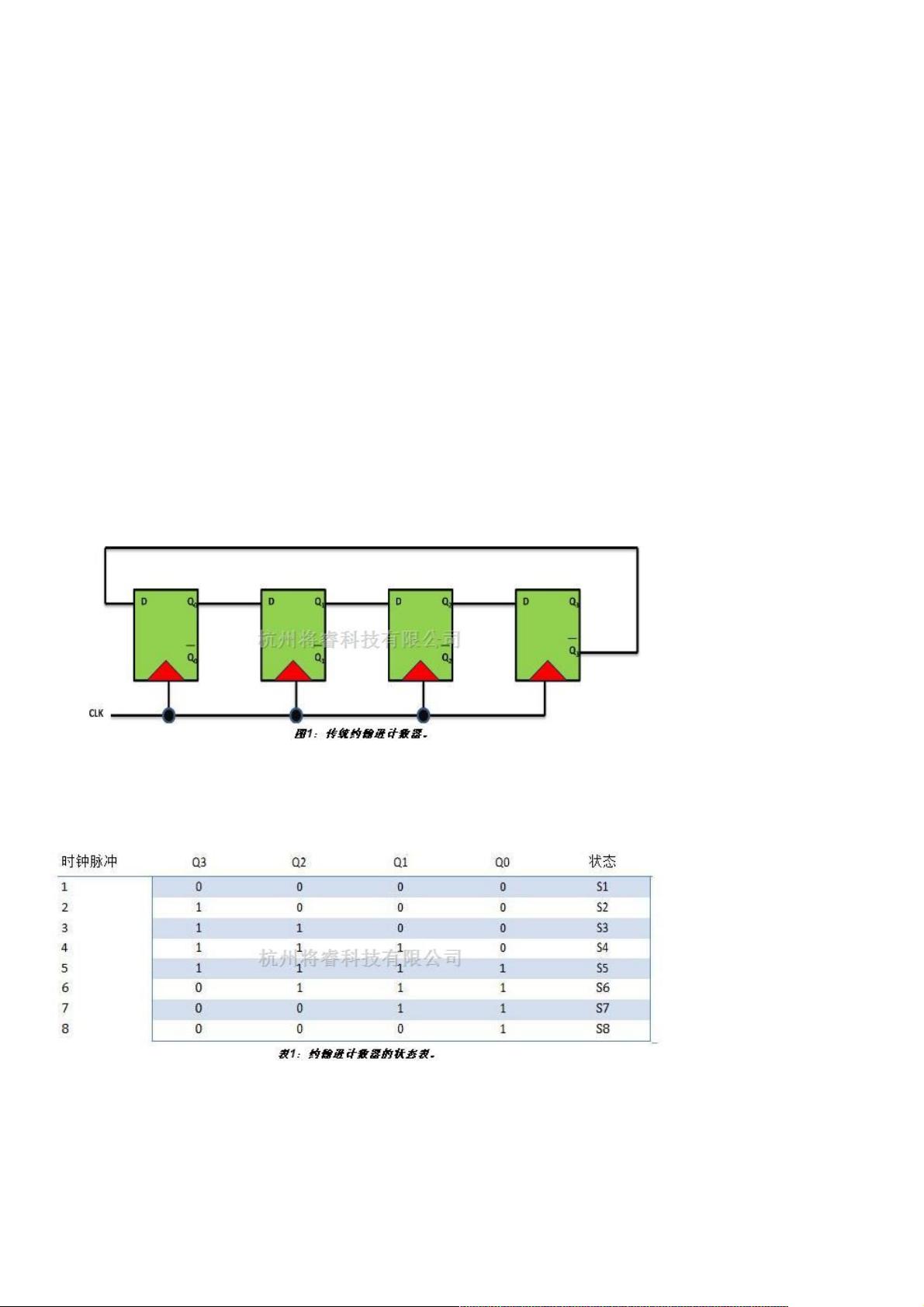

门控时钟技术是一种优化功耗的方法,它允许在不需要时关闭时序电路的时钟信号,进而减少无效功耗。例如,在约翰逊计数器的设计中,通过控制时钟信号的开关,可以确保只有在必要的时候才进行数据传输和状态变化,从而节省能量。约翰逊计数器作为一种特殊的移位寄存器,能够生成特定的数据序列,对于多种重要应用如D/A转换器、有限状态机(FSM)和时钟分频器等有着广泛的应用价值。

时钟分频是许多数字系统中的基础功能,用于将高频率信号转换为较低频率的信号,满足不同组件的不同速度需求。传统的多级分频器可能造成不必要的功耗,而使用带有门控时钟的约翰逊计数器系统可以实现动态的、可编程的分频,通过减少不必要的时钟切换,降低功耗。文章提出了一个可提供8到38之间任意偶数分频因子的门控时钟约翰逊计数器设计,这在系统级集成中提供了更高的灵活性和能效。

设计的实施细节包括对触发器的布局和门控时钟的控制逻辑,以及如何通过调整门控条件来实现不同分频因子。这种设计的优势在于,它减少了硬件资源的使用,同时降低了功耗,提高了系统性能。然而,也需要注意,门控时钟可能导致时序分析和故障检测的复杂性增加,因为时钟的开启和关闭需要精确的控制,否则可能会引入额外的延迟和不确定性。

电源技术中的基于门控时钟的低功耗时序电路设计是当前集成电路设计的重要研究方向。通过巧妙地应用约翰逊计数器和门控时钟,可以创建出更高效、节能的数字系统,以满足现代移动设备和物联网(IoT)设备的严苛要求。这种技术的持续发展和优化将对未来的电子设计产生深远影响,推动低功耗电子产品的创新。

2020-08-29 上传

2009-09-14 上传

2020-10-19 上传

2023-07-11 上传

2024-05-10 上传

2023-03-28 上传

2023-06-23 上传

2024-11-25 上传

2024-11-08 上传

weixin_38672940

- 粉丝: 5

- 资源: 970

最新资源

- BangBang教育:家庭作业

- 145026,c语言种子解析下载源码,c语言

- AutoSplitterJourney

- 一个个人文件管理系统的源码脚手架r-pan基于此脚手架搭建快速搭建个人文件管理系统

- gchisto:GC日志分析工具,网上不容易找到原始码,这里备份一个。不确定工具是否正确,不确定是否有时间研究

- H5手机端免费问卷调查平台系统aspnet源码

- assistant:自动化的个人助理,可帮助您前进并跟踪您的成绩,以获得良好生活

- 虚拟DVD精灵 VirtualDVD 9.2 中文.zip

- evikd,c语言项目文档以及源码,c语言

- tts-40k-roller:台式模拟器上用于战锤40k的压模辊

- 【ssm管理系统】实现的在线考试系统.zip

- 音听故事个人网站

- cacheman-file:Node.JS的文件缓存库,还有cacheman的缓存引擎

- OLML:各种日常的自动化办公工具

- nix-container-perfzero:在XSEDE环境中运行perfzero基准测试的容器

- TORZ,c语言开源软件源码下载,c语言