Vivado配置与ModelSim集成及器件库编译教程

版权申诉

DOCX格式 | 842KB |

更新于2024-08-20

| 141 浏览量 | 举报

"该文档详细介绍了如何在Vivado中配置ModelSim仿真工具,并进行器件库的编译,以便在Vivado环境下使用ModelSim进行设计仿真。"

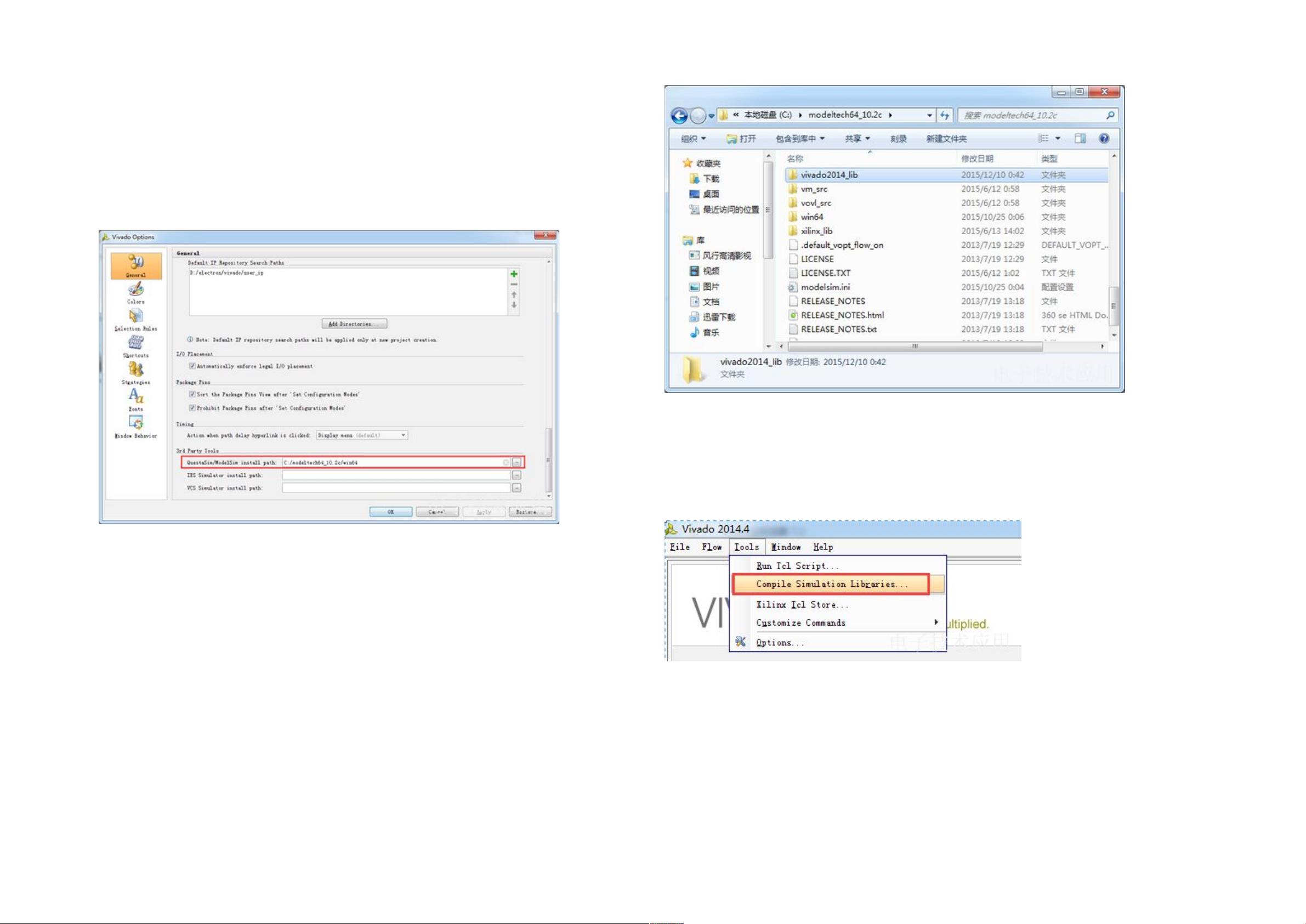

在Vivado与ModelSim的集成过程中,首先需要在Vivado的工具选项中设置ModelSim的安装路径。这可以通过选择菜单“Tools” -> “Options”,然后在“General”选项卡的“QuestaSim/ModelSim install path”栏中指定ModelSim的安装位置。这个步骤至关重要,因为它允许Vivado识别并调用ModelSim作为仿真器。

接下来,为了进行器件库的编译,需要在ModelSim的安装目录下创建一个新的文件夹,例如名为“vivado2014_lib”。创建这个文件夹的目的是存储Vivado编译的器件库。然后通过Vivado的“Tools” -> “CompileSimulationLibraries”命令启动器件库编译过程。在此过程中,需要设定仿真工具为ModelSim,语言、库和器件家族可根据具体需求调整,但通常默认设置为“Language: All”,“Library: All”,“Family: All”。编译库的路径应指向之前创建的“vivado2014_lib”文件夹,同时设置ModelSim的执行文件路径。完成这些设置后,点击“Compile”以启动器件库编译。

器件库编译完成后,会生成一个编译报告,确认无警告和错误。这表明器件库编译成功。编译的器件库将存储在指定的“vivado2014_lib”文件夹中,可以查看到生成的库文件。

最后,为了在Vivado中使用ModelSim进行仿真,需要在每个新工程的仿真设置中进行相应配置。可以通过“Flow” -> “SimulationSettings”或者在流程向导中选择“SimulationSettings”来设定。这些设置确保Vivado能够正确调用已配置的ModelSim和编译好的器件库,从而进行设计的仿真验证。

这个文档提供了详尽的步骤指导,帮助用户在Vivado中配置ModelSim并编译器件库,使得VHDL或Verilog等硬件描述语言设计能够在ModelSim环境中进行功能和时序仿真,是学习和工作中非常实用的操作指南。

相关推荐

lulusuhua

- 粉丝: 0

- 资源: 11万+