FPGA时序分析实战:七天掌握Altera时序设计

"该资源是一份关于学习FPGA(Field-Programmable Gate Array)的教程,特别是针对Altera公司的产品。教程分为基础篇和时序篇,旨在帮助读者在七天内掌握FPGA的基本使用和时序分析。时序篇详细介绍了时序分析的关键概念,包括同步逻辑时延模型、时序检查公式、Altera器件的时序模型以及如何使用Timequest时序分析器进行设计约束和分析。"

在《通向FPGA之路---七天玩转Altera之时序篇V1.00》中,作者首先介绍了时序分析的基本概念。时序分析是确保数字系统正确运行的核心部分,它关注的是数据在时钟周期内的传输和处理。同步逻辑时延模型包括了时钟抖动与偏斜,这两个因素会影响信号的精确时序。建立时间和保持时间是保证数据正确捕获的关键参数,前者是指数据必须在时钟边沿之前到达,后者是指数据必须在时钟边沿之后保持稳定的时间。恢复时间和移除时间则涉及到数据路径中的延迟和清除,确保数据在正确的时间窗口内可用。

接着,教程详细讲解了时序分析的基本公式,如建立时间、保持时间、恢复时间和移除时间的检查,这些都是确保设计满足时序要求的必要步骤。多周期路径检查允许在某些路径上放宽时序限制,提高设计的灵活性。同时,了解Altera器件的时序模型有助于理解其内部工作原理和优化设计。

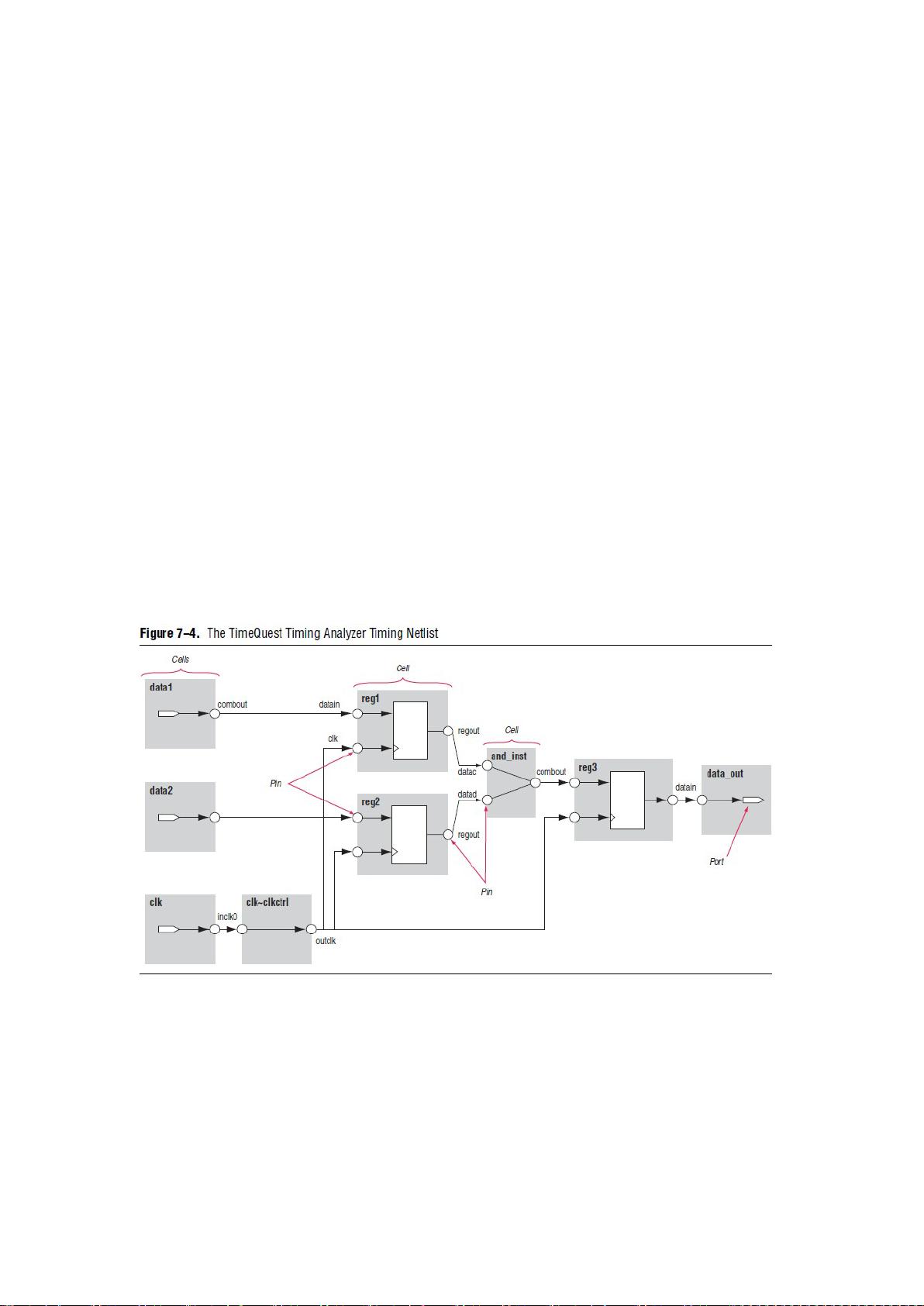

教程还深入讨论了基本单元与paths,这些是构成FPGA设计的基础元素,理解它们对于时序分析至关重要。时序优化方法和关键路径的识别是提升设计性能的关键。此外,时序约束的几种方法被介绍,包括对Tsu(建立时间)和Tco(传播时间)的简单约束,这些都是在Timequest时序分析器中设置设计规则的关键。

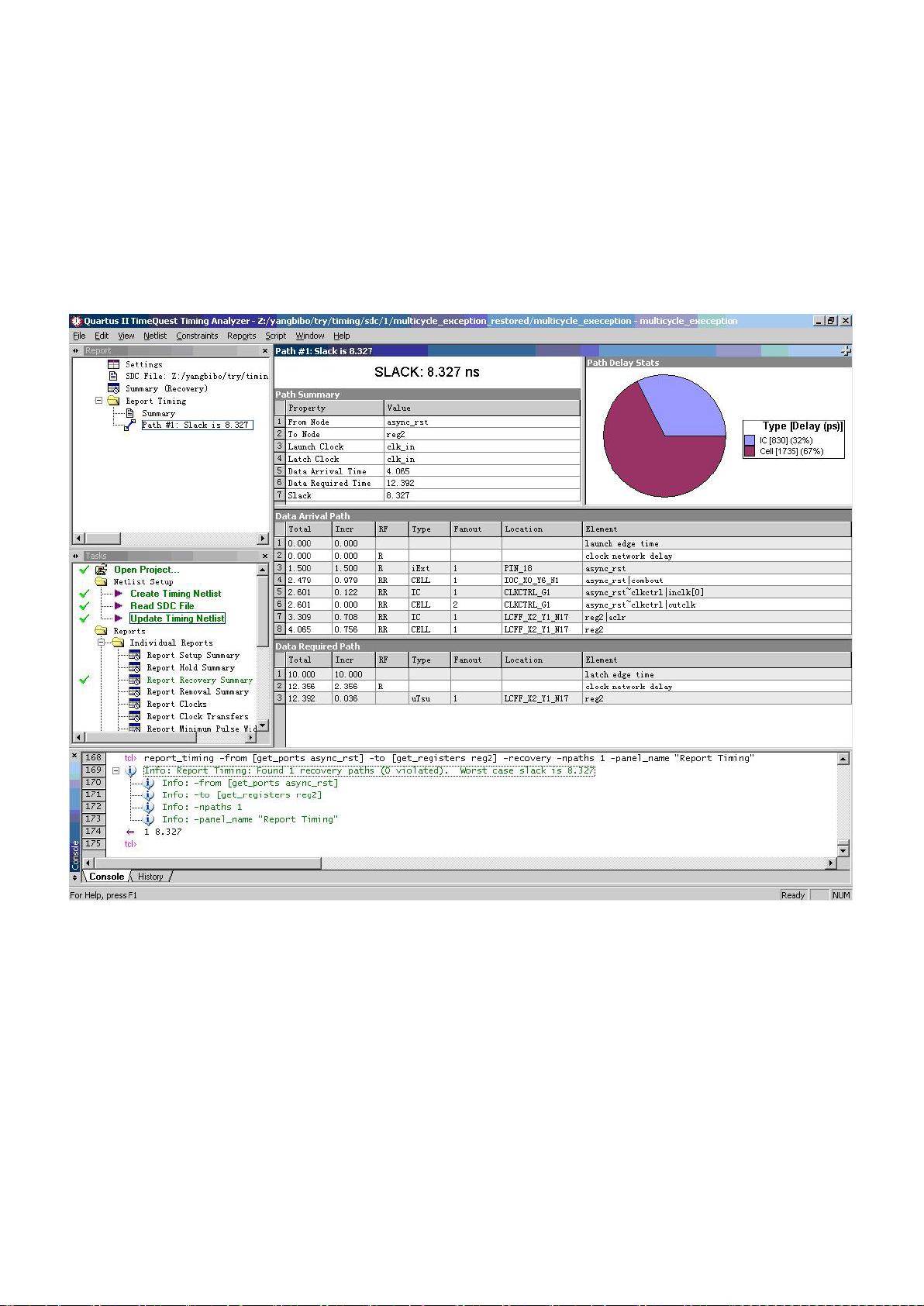

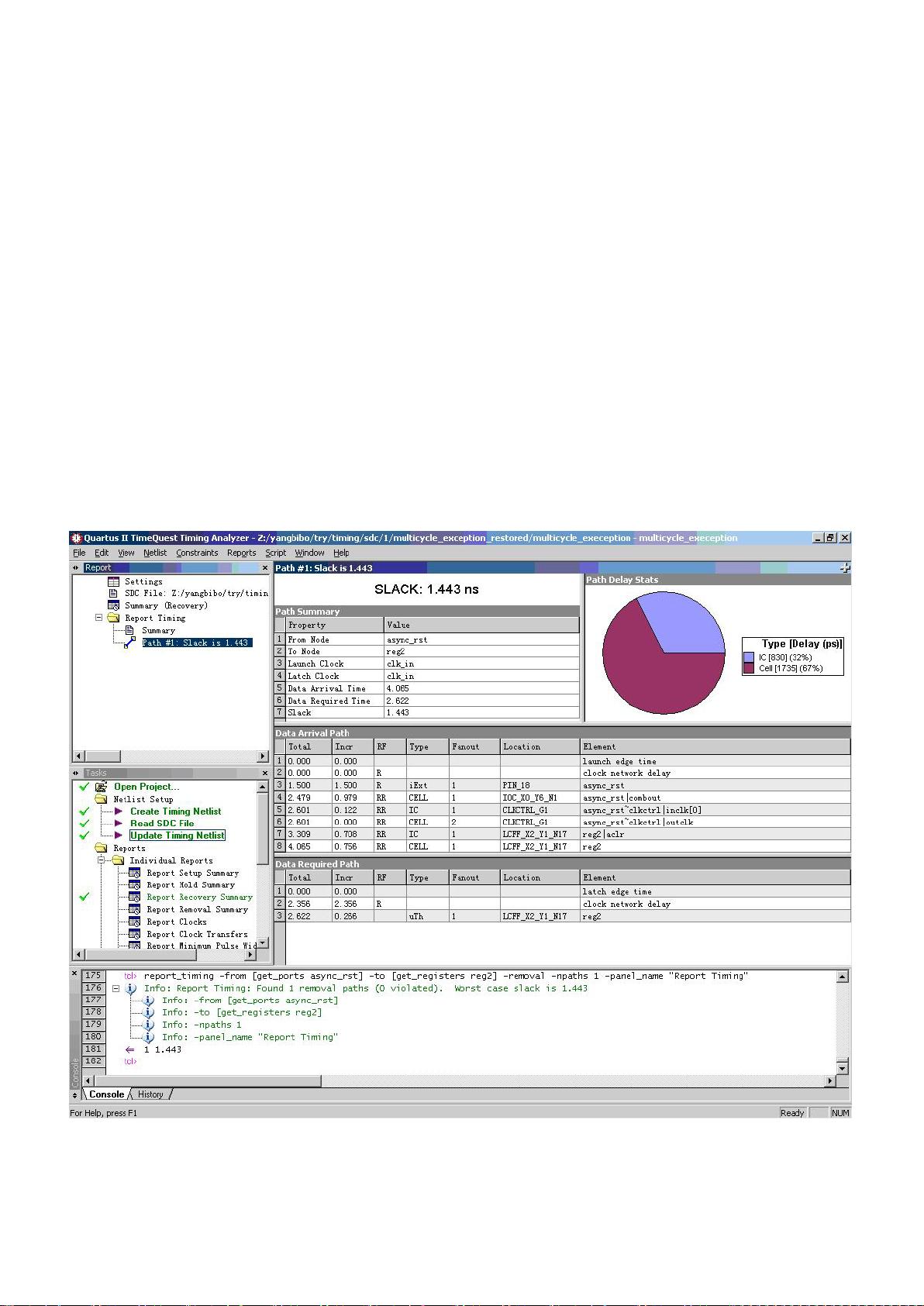

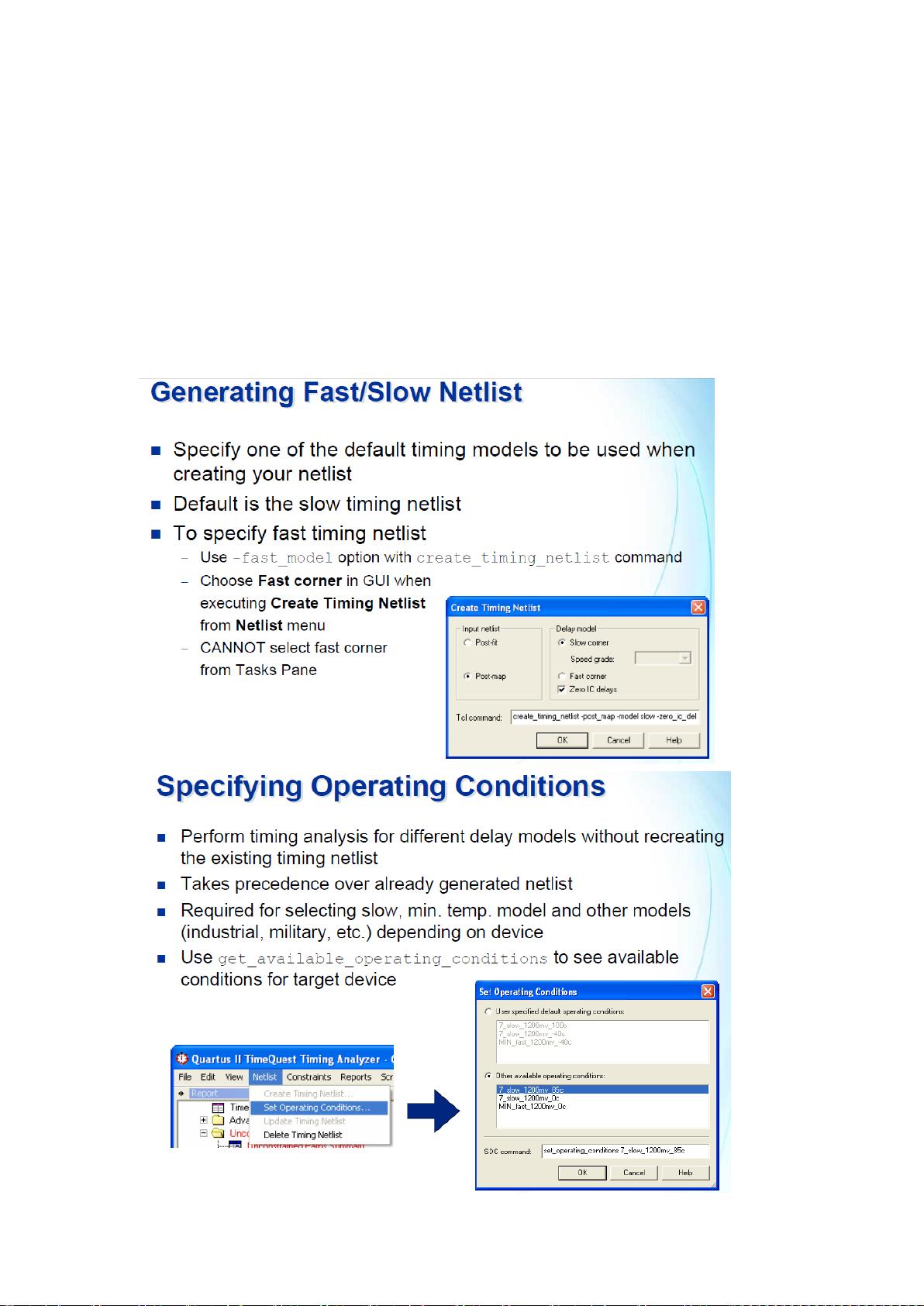

Timequest时序分析器是Altera工具链的重要组成部分,用于分析和约束设计的时序。教程详细阐述了如何使用Timequest进行基础操作,包括时序约束和分析流程、GUI界面的使用、时序波形图的理解、时序余量的计算等。在时序约束部分,详细介绍了各种时钟约束,如创建时钟、生成时钟、PLL时钟、自动检测和创建时钟,以及默认约束、时钟延迟、时钟不确定性等。此外,还涉及了输入/输出接口的时序约束,如组合逻辑接口和同步接口的约束,以确保数据传输的正确性。

这份教程为初学者提供了全面的FPGA时序分析知识,通过学习,读者可以掌握FPGA设计中的时序关键点,以及如何利用工具进行有效的时序分析和优化。

2015-10-08 上传

2022-04-22 上传

2022-04-22 上传

2021-10-14 上传

2012-02-22 上传

2014-11-03 上传

2011-09-23 上传

fengzutian

- 粉丝: 1

- 资源: 4

最新资源

- vb语言程序设计教程.zip

- sjasmplus:SJAsmPlus

- A06:作业6

- GnomeNibus-开源

- message-franking-tester:实施不同的邮件盖章方案和性能分析测试仪

- 机器学习python标记工具-Labelimg2024

- React-Portfolio:我的一小部分作品,用React重写

- MM32SPIN0x(s) 库函数和例程.rar

- goApi

- cuetools-开源

- Veni-Vidi-Voravi

- website:Terre Tropicale公共网站

- Main:基于struts2库存管理系统Android端

- Another-React-Lib:只是另一个充满可重用组件的React库

- 华为简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 原型