ARM内存管理单元详解:MMU、TLB与页表

版权申诉

118 浏览量

更新于2024-07-08

收藏 1MB PPTX 举报

"该文档是关于ARM内存管理单元的学习资料,涵盖了ARM处理器的内存地址范围、分页机制、TLB和地址转换表的功能,以及CP15寄存器在MMU中的作用,还介绍了ARM MMU的2级页表结构。"

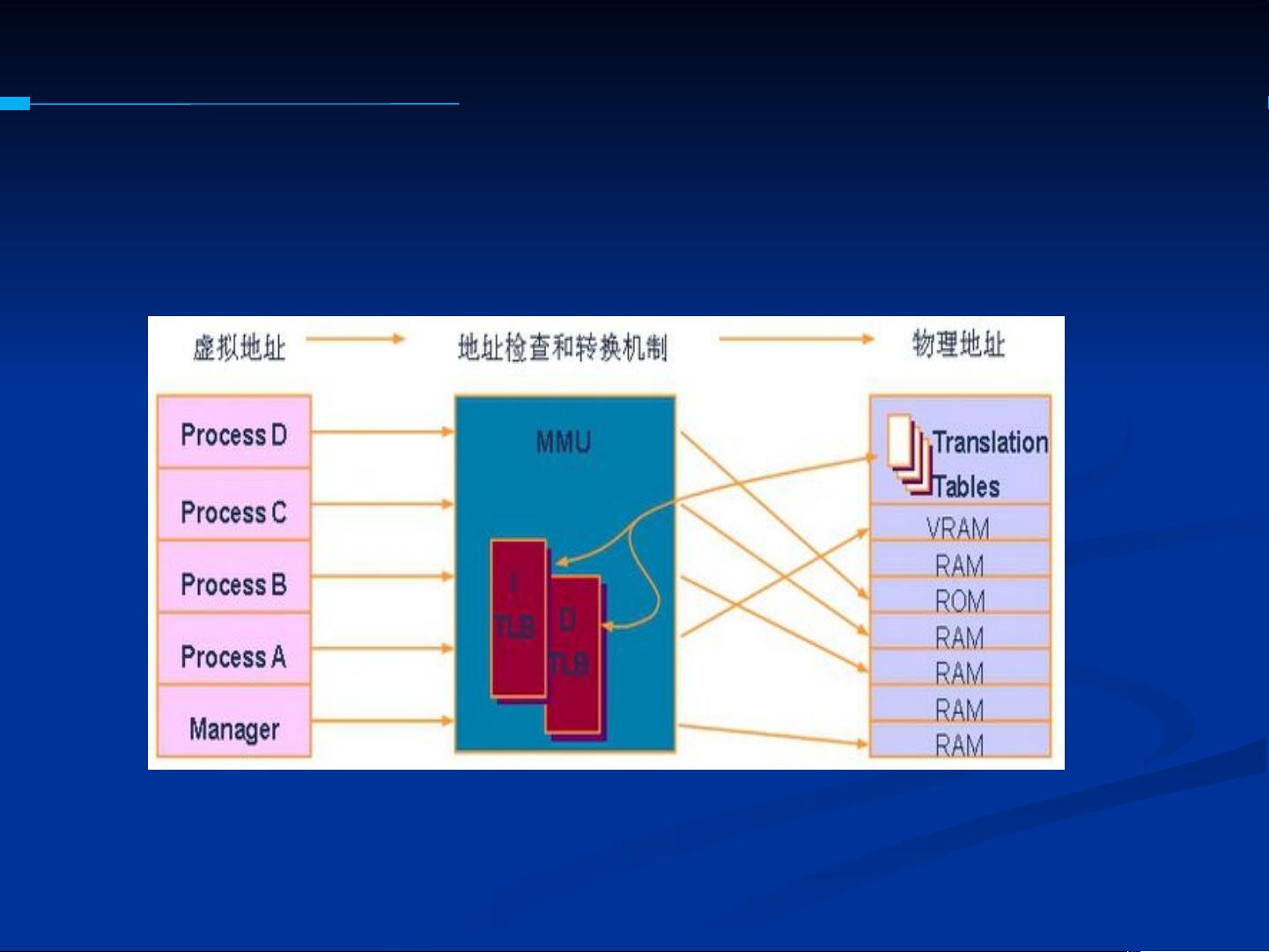

在了解ARM架构的内存管理单元(Memory Management Unit, MMU)时,首先要明白地址范围是由CPU的位数决定的。例如,一个32位的CPU能够寻址的最大地址空间为4GB。内存管理的关键在于虚拟地址和物理地址之间的映射,这通常通过分页机制实现。分页机制将虚拟地址空间划分为等大的页,同时物理地址空间也按页进行划分,页的大小通常是4KB或其他固定值。

TLB(Translation Lookaside Buffer)是MMU的重要组成部分,它是一种高速缓存,存储最近使用的虚拟地址到物理地址的转换。当CPU试图访问内存时,首先会在TLB中查找转换信息。如果找到,可以直接获取物理地址,否则需要查询地址转换表。地址转换表通常是一个多级结构,如386处理器中的页目录表和页表,用于将线性地址转换为物理地址。在ARM架构中,若TLB未命中,会查找2级页表结构,即一级页表(L1)和二级页表(L2)。

CP15是ARM处理器中的协处理器寄存器,其中C8寄存器用于控制TLB内容的清除,而C10寄存器则用于控制TLB内容的锁定。在具有独立指令TLB和数据TLB的系统中,可以分别对这两个部分进行操作。寄存器的选择通过`opcode_2`字段来决定。

ARM MMU的2级页表结构提供了一种高效的方式来进行地址映射。一级页表包含不同类型页表项,如1MB的大页转换项或指向二级页表的目录项。二级页表进一步细化了地址映射,使得内存管理更加灵活。

在多用户多进程的现代操作系统中,MMU确保了每个进程都有自己独立的地址空间。操作系统通过MMU分配不同的地址区域给每个进程,使得相同的虚拟地址在不同进程中可能映射到不同的物理地址,从而实现进程间的隔离和安全性。

这份ARM内存管理单元的学习资料深入探讨了MMU的工作原理,包括地址转换机制、TLB的运作以及相关的CP15寄存器,对于理解ARM架构下的内存管理和系统级编程有着重要的参考价值。

2021-09-29 上传

2021-10-02 上传

2022-04-17 上传

2023-02-26 上传

2023-05-26 上传

2023-05-26 上传

2023-03-21 上传

2024-10-30 上传

2023-05-29 上传

yingyingyiwan

- 粉丝: 0

- 资源: 12万+

最新资源

- loopstudios:响应式网页旨在训练HTML,CSS和少量JavaScript

- ga_blog

- 每周:每周

- Contour plot based on Delaunay with linear interpolation:Contour plot based on Delaunay triangulation with linear interpolation between triangles-matlab开发

- Lotide

- study:我的最佳实践总结

- chrispearce.co:个人网站

- groups群的复合参数化:使用复合参数化生成unit矩阵和特殊unit矩阵。-matlab开发

- rodrigoSilva23

- CeoClick项目

- elive-开源

- TowerDefence:根据教程学习塔防游戏

- Laurel-genes

- lumberjack:伐木工人是Go的日志滚动包

- pmap - 参数空间稳定性映射套件:在连续时间系统的参数空间中查找 Hurwitz 稳定性区域。-matlab开发

- OPPOR9mh原厂维修图纸.zip