UVM 1.1技术参考手册:通用验证方法

需积分: 9 160 浏览量

更新于2024-07-14

收藏 3.56MB PDF 举报

"UVM_1.1_Class_Reference_Final_06062011(1).pdf"

本文档是关于Universal Verification Methodology (UVM) 1.1版本的类参考指南,发布于2011年6月。UVM是一种基于SystemVerilog的行业标准验证方法论,旨在提供一种可重用、可扩展和参数化的验证环境,用于硬件设计的验证工作。

在系统级验证中,UVM扮演着至关重要的角色,它提供了一套全面的验证组件和机制,包括代理(agent)、序列器(sequencer)、监视器(monitor)和测试平台(testbench)。这些组件通过接口和消息传递机制协同工作,实现了验证环境的模块化和复用性。

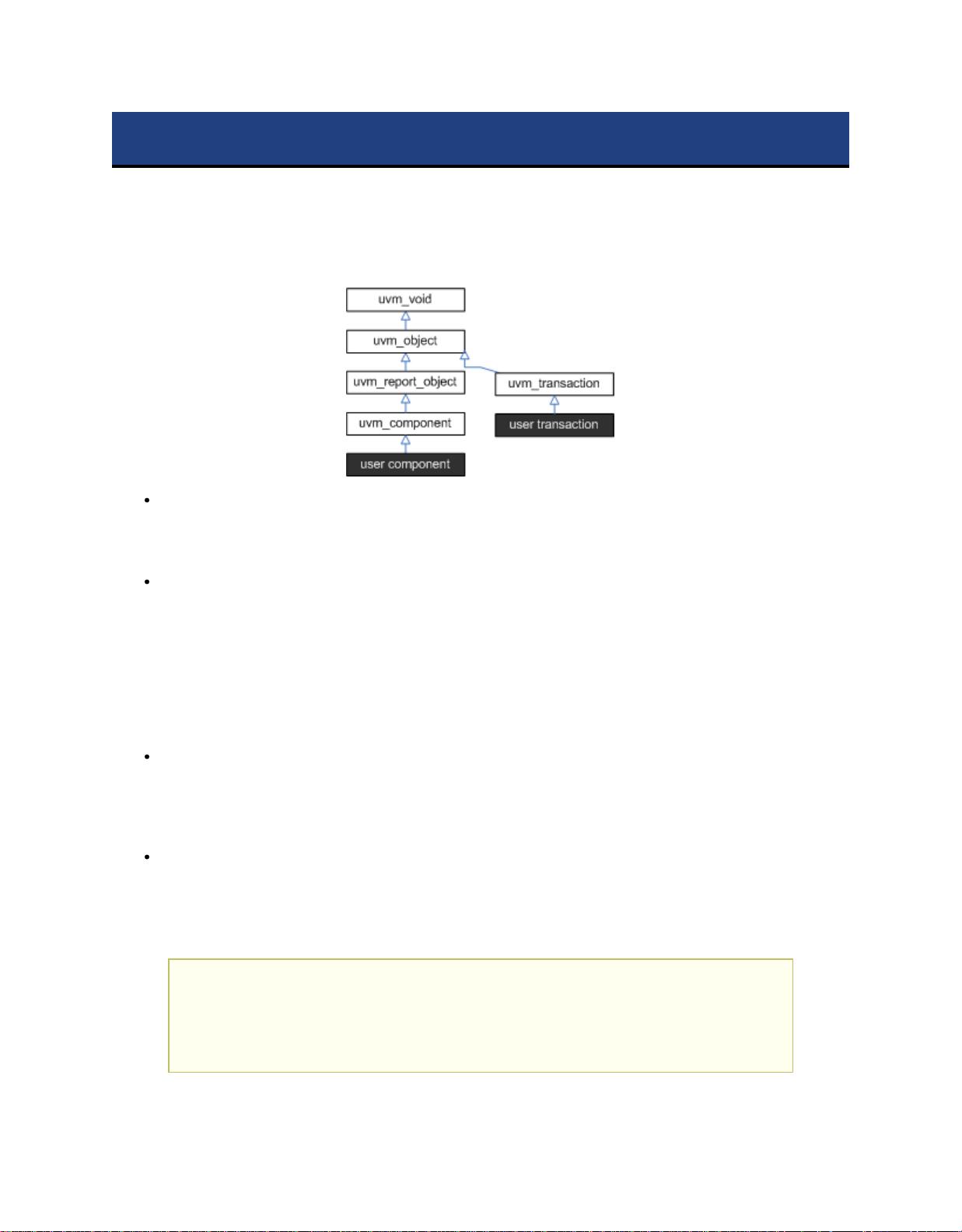

1. **UVM基础组件**

- **UVM类层次**:UVM的核心类包括了基类、抽象类和具体实现类。例如,uvm_component类是所有UVM组件的基础,它提供了基本的生命周期管理、名字管理和报告功能。

- **代理(Agent)**:代理是连接被验证模块和测试平台的桥梁,包含了一个序列器、一个或多个监视器以及驱动和响应链接。

- **序列器(Sequencer)**:序列器控制激励的生成和调度,允许不同的序列在同一时间运行,并处理它们之间的优先级和冲突。

- **监视器(Monitor)**:监视器负责监听被验证模块的行为,收集数据并报告到测试平台。

- **测试平台(Testbench)**:测试平台是整个验证环境的框架,由根组件(root component)和其他组件组成,它负责设置环境、启动验证过程和收集结果。

2. **UVM机制**

- **消息传递**:UVM使用TLM(Transaction Level Modeling)来处理组件间的通信,包括端口(port)和出口(export)的概念,以及传输(transfer)对象的定义。

- **事件和队列**:UVM提供了事件处理机制和队列,用于同步组件操作和异步消息传递。

- **工厂(Factory)**:UVM的类工厂允许动态实例化和配置组件,增强了复用性和灵活性。

- **覆盖(Coverage)**:UVM提供了内置的覆盖模型和工具,帮助分析验证的覆盖率,评估设计验证的完整性。

3. **UVM流程**

- **配置(Configuration)**:UVM的配置机制允许在不修改代码的情况下改变组件的属性和结构。

- **运行时环境设置**:包括随机化种子、时间单位、报告级别等,可在运行时动态调整。

- **启动和结束阶段**:UVM定义了一系列的开始和结束阶段,如build、connect、run、end_of_simulation等,确保组件的正确初始化和清理。

4. **合规性和移植性**

- UVM遵循Accellera组织的标准开发流程,确保了其在不同项目和团队间的互操作性和一致性。

- UVM的文档强调,虽然标准提供了统一的方法论,但使用标准本身是自愿的,且Accellera不对标准中的信息准确性和使用后果承担责任。

UVM 1.1版的类参考指南详细阐述了每个类的功能、方法和属性,是理解UVM工作原理和实现验证环境的关键资源。通过深入学习和实践,设计者能够创建高效、可维护的验证环境,提高硬件验证的质量和效率。

2014-08-13 上传

2015-09-16 上传

2020-09-12 上传

2011-06-17 上传

2022-09-14 上传

2021-08-26 上传

2022-07-14 上传

173 浏览量

qq_41451077

- 粉丝: 0

- 资源: 2

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库