无需处理器:嵌入式系统中利用SPI控制FPGA Avalon总线的简易方法

11 浏览量

更新于2024-09-03

收藏 819KB PDF 举报

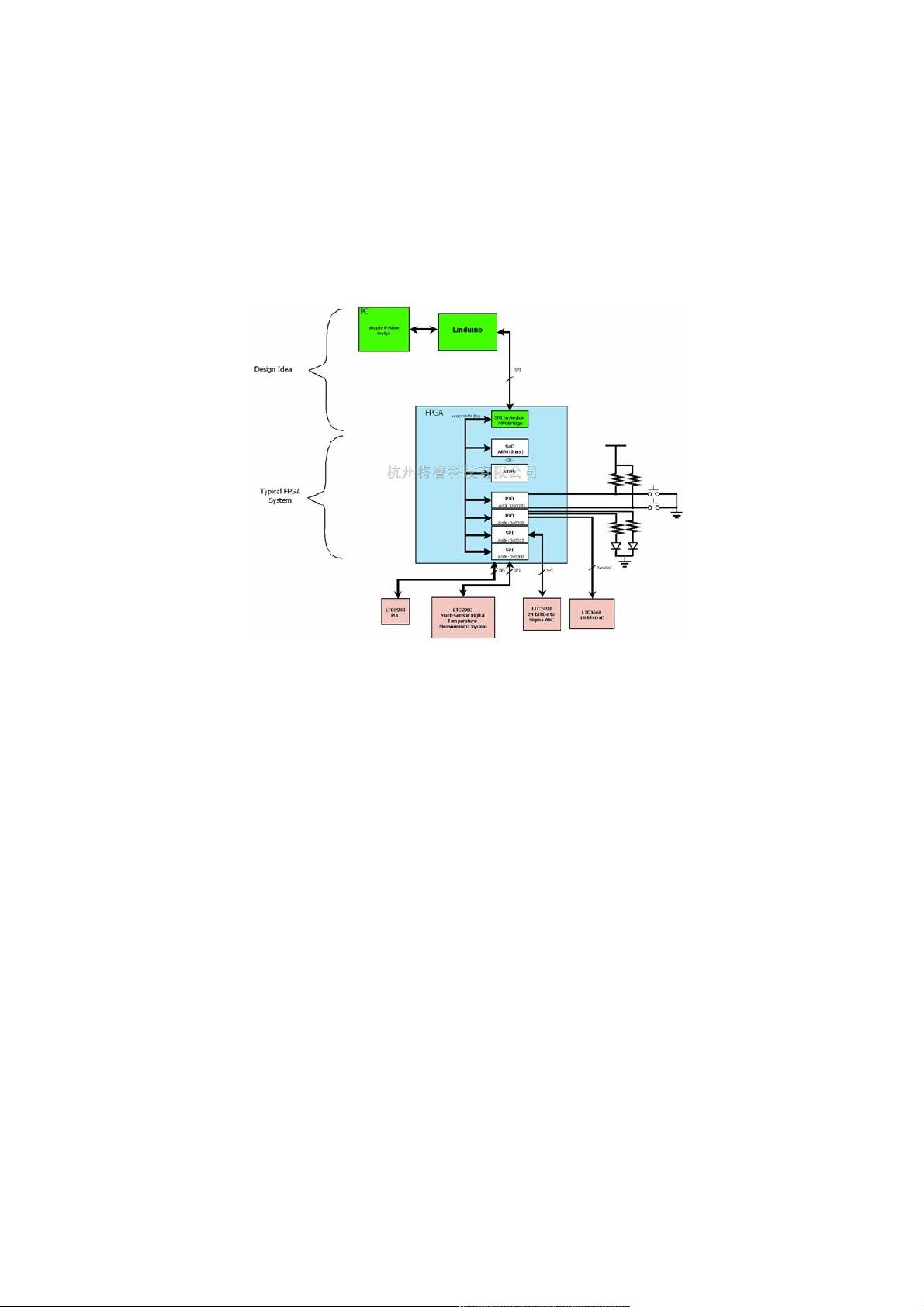

嵌入式系统/ARM技术中的不用处理器控制FPGA总线的方法是一种新兴的设计策略,特别是在FPGA(Field-Programmable Gate Array)设计中,旨在减少对嵌入式处理器的依赖,以提升调试效率和简化硬件工程师的工作流程。传统的方案倾向于使用Nios这样的软处理器,如Altera的系统级芯片(FPGASoC)中集成的处理器,它们通过 Avalon内存映射(MM)总线与外设通信,如图1所示的典型Altera FPGA系统。

Avalon MM总线提供了一种标准化的方式来连接和管理外设,使得系统设计更加模块化。然而,这需要深厚的编程背景和熟悉复杂的工具链,这对于硬件工程师来说可能是一项挑战,特别是当他们希望在没有过多软件干预的情况下直接操控外设时。例如,硬件工程师可能会想要直接控制LTC6948的小数分频锁相环频率,LTC1668的电压设置,或者读取LTC2498和LTC2983的相应数据。

为了解决这个问题,本文设计了一个基于Altera SPI的SlavetoAvalon MM桥,这个桥的作用是充当SPI信号和Avalon MM总线之间的中介,允许工程师无需处理器直接进行操作。这种设计的优势在于,它不会对原系统架构造成干扰,且可以与嵌入式处理器共存,提高了灵活性和易用性。

图2展示了如何通过高亮部分的代码和反向工程,利用Python脚本来实现这一功能。尽管Altera提供了SPI-Avalon MM桥的参考设计,但这些文档往往专注于Nios处理器的应用,而非作为SPI主设备的用途。实际上,更实用的选择可能是使用像凌力尔特(Lin

duino)这样的微控制器,它继承了Arduino处理器的功能,且支持直接连接到LT演示板,这样就避免了对Nios的过度依赖。

总结来说,嵌入式系统/ARM技术中的不用处理器控制FPGA总线的方法,如Altera的SPI桥设计,为硬件工程师提供了一种简化外设控制的途径,降低了对高级软件技能的需求,同时也强调了选择合适工具和设备的重要性。这对于那些寻求高效调试和易于维护的系统设计者来说,是一个重要的技术考虑。

161 浏览量

127 浏览量

222 浏览量

2024-11-02 上传

2024-11-05 上传

328 浏览量

2024-11-28 上传

260 浏览量

2024-10-27 上传

weixin_38517113

- 粉丝: 3

最新资源

- 流浪汉环境性能比较:Virtualbox vs Parallels

- WatchMe项目使用TypeScript进行开发的介绍

- Nali:全面支持IPv4/IPv6离线查询IP地理及CDN信息工具

- 利用pdfjs-2.2.228-dist实现零插件PDF在线预览技术

- MATLAB与jEdit集成:实用工具包发布

- Vagrant、Ansible和Docker搭建Django应用环境

- 使用Delphi更改计算机名称的详细教程

- TrueNAS CORE中iocage-homeassistant插件的高级安装方法

- rack程序:命令行工具高效处理天气雷达数据

- VS2017下实现C# TCP一对多通信程序源码

- MATLAB项目管理器:快速切换与路径管理

- LightDM GTK+ Greeter设置编辑器的Python图形界面介绍

- 掌握CSS技巧,提升网页设计美感

- 一维RCWA算法在matlab中的实现与应用

- Hot Reload插件:提升Flutter开发效率的Vim工具

- 全面掌握Dubbo:Java面试题及详细答案解析