SK DDR3L H5TC系列:高密度低功耗内存技术详解

需积分: 19 47 浏览量

更新于2024-07-19

收藏 492KB PDF 举报

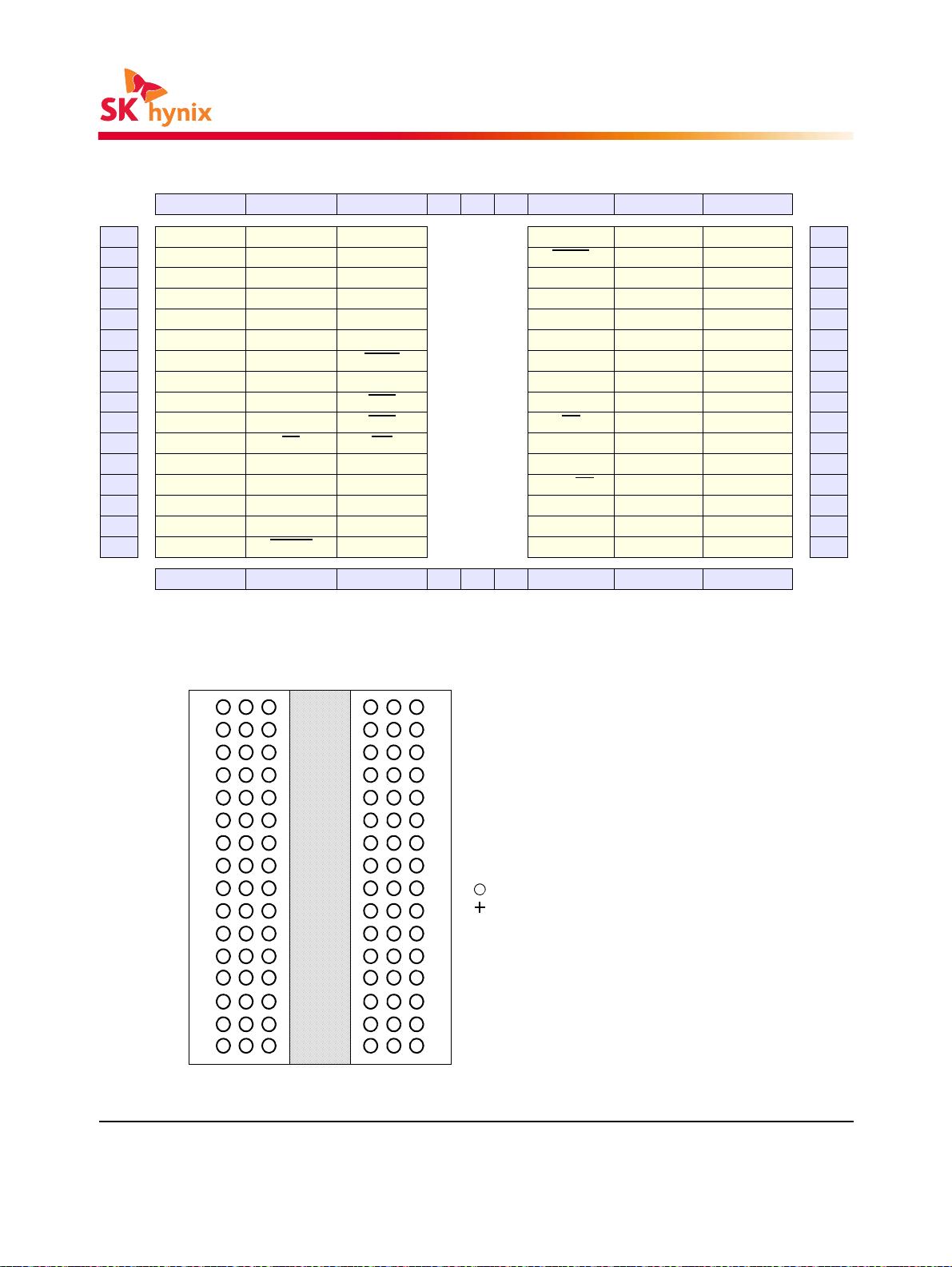

本文档主要介绍了SK Hynix生产的4Gb DDR3L SDRAM系列,包括H5TC4G43AFR-xxA、H5TC4G83AFR-xxA和H5TC4G63AFR-xxA。DDR3L是低功耗的双数据速率III(DDR3L)同步动态随机存取内存,特别适合于需要高密度存储、高带宽和在1.35V低电压下运行的主内存应用。这种内存具有向1.5V DDR3环境的向下兼容性,无需任何改动,用户可以通过SPD(Serial Presence Detect,即芯片内置的数据表)获取详细信息。

这些4Gb DDR3L SDRAM的特点在于其全同步操作,参考时钟信号的上升和下降沿。所有地址和控制输入在时钟信号的上升沿(下降沿)被锁存,而数据、数据选通和写入数据屏蔽信号则在时钟的上下沿进行采样。内部数据路径采用流水线设计并预取8位数据,以实现极高的带宽性能。

文档还提到了产品的一些基本信息,如无铅和无卤素(RoHS合规),以及修订历史。最初的版本发布于2012年10月,1.0版本在2013年4月发布,说明SK Hynix保留随时更改产品规格的权利。值得注意的是,用户应查阅最新的文档以获取最准确的信息。

在设计和选择这些内存模块时,了解这些特性对于确保系统兼容性和优化性能至关重要。同时,对于制造商提供的技术规格、工作条件和兼容性指导,工程师和系统设计师应予以充分考虑。

137 浏览量

1364 浏览量

2022-07-15 上传

2022-07-15 上传

138 浏览量

2022-07-15 上传

2021-08-12 上传

2021-03-11 上传

2021-02-12 上传

anonymous_de

- 粉丝: 17

- 资源: 15

最新资源

- jquery开关按钮基于Bootstrap开关按钮特效

- merkle-react-client:客户

- 财务管理系统javaweb项目

- DOM-Parsing:DOM解析和序列化

- FastReport v6.7.11 Enterprise installer .zip

- pid控制器代码matlab-AutomatedBalancingRobot:自动平衡机器人是一个项目,其中建造了一个两轮机器人,并将其编程为

- 基于MATLAB模型设计的FPGA开发与实现.zip_UBK_matlab与fpga_simulink模型_struck9hw_

- ubiq:基于HugSQL和GraphQL的Web应用程序,移动部分最少

- 行业文档-设计装置-一种折叠式防滑书立.zip

- 意法半导体参考文献及软件资料.7z

- LoRa-High-Altitude-Balloon:这是蒙大拿州立大学LoRa小组顶峰项目的存储库,该项目是蒙大纳州太空资助财团BOREALIS实验室的项目。 以下代码在定制板上运行,该定制板上旨在收集高空气球有效载荷上的大气数据

- BW_Anal-开源

- nuaa_check_action:inuaa打卡,基于GitHub Action的南航校内,校外打卡

- alex_presso

- perf:PERF是详尽的重复查找器

- 行业文档-设计装置-一种折叠式包装纸箱.zip