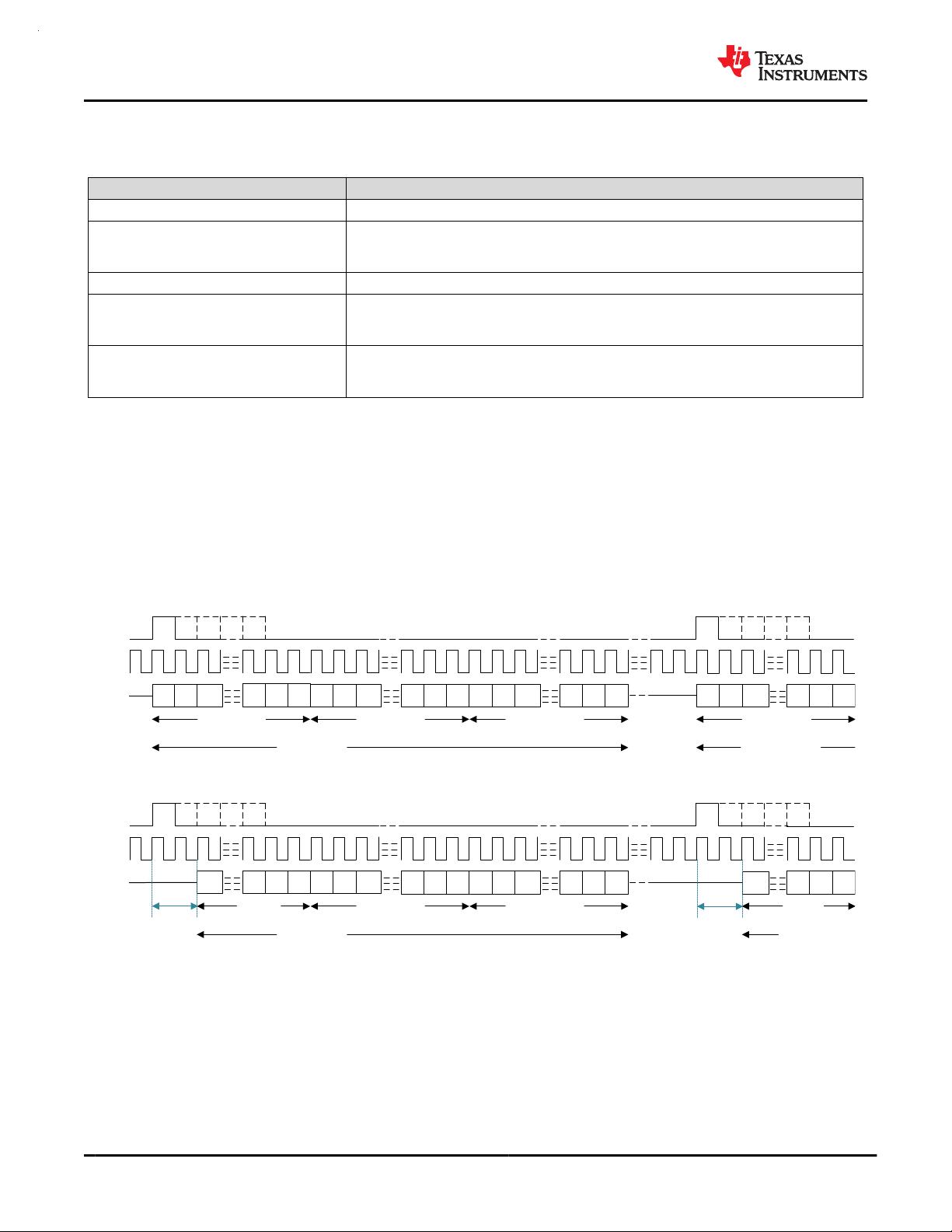

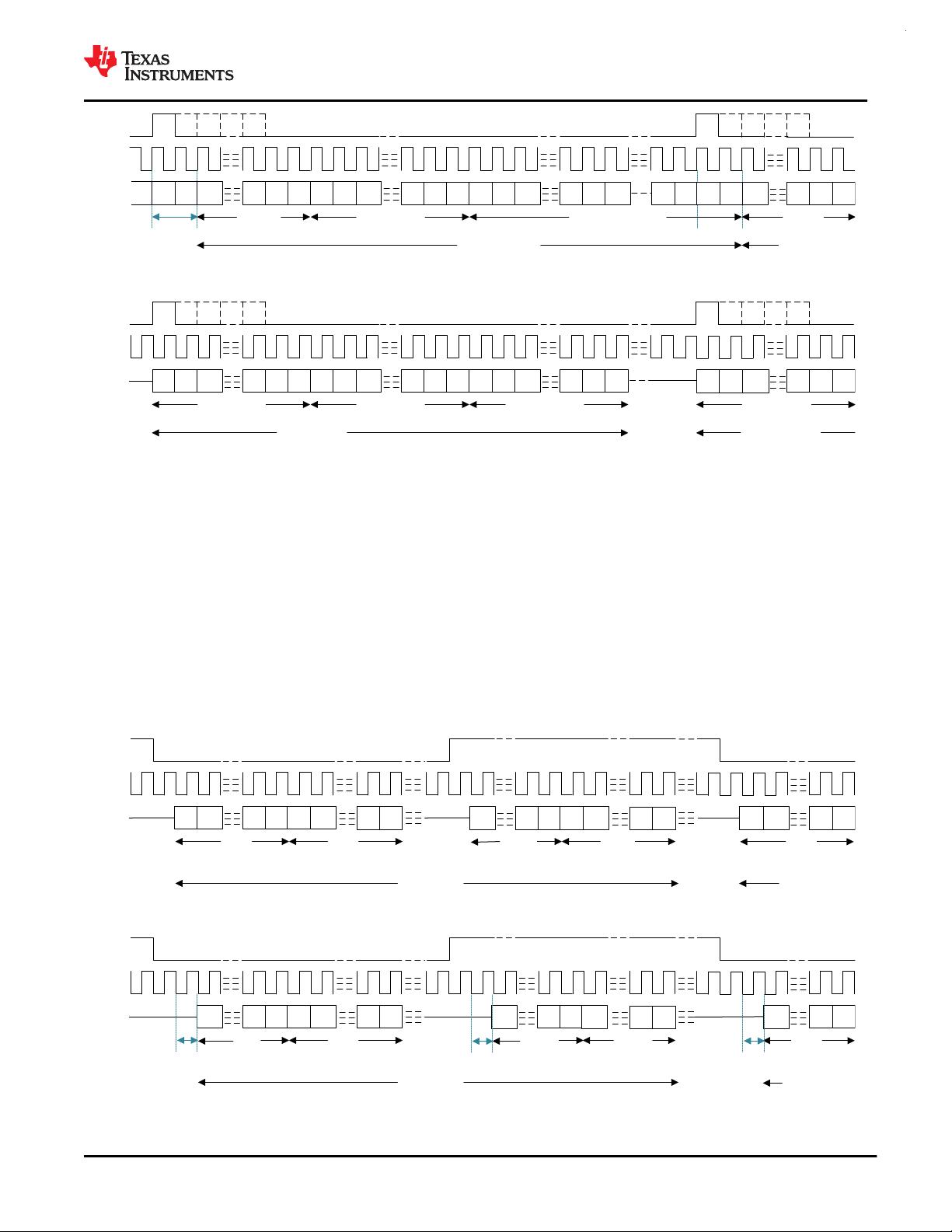

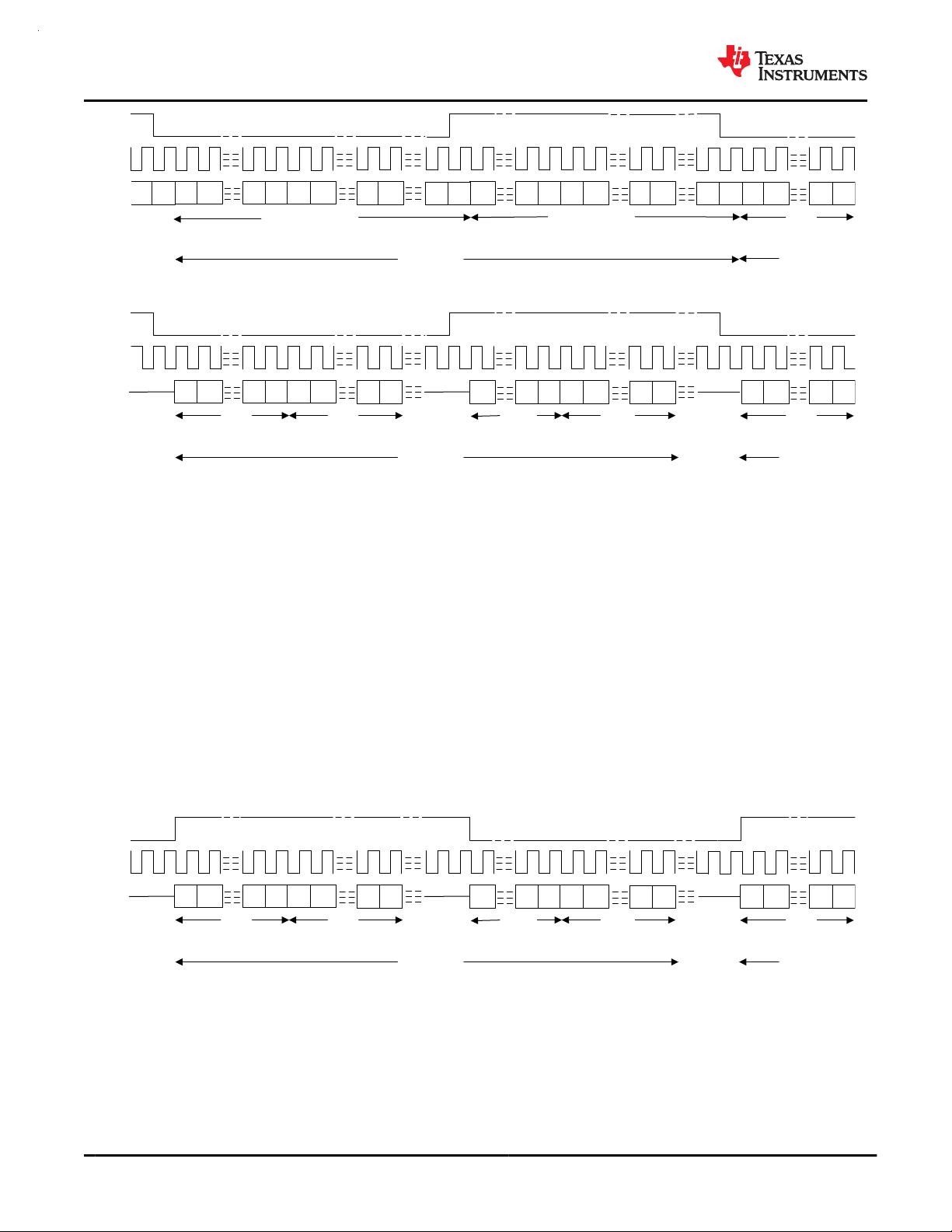

The bus protocol TDM, I

2

S, or left-justified (LJ) format can be selected by using the ASI_FORMAT[1:0]

(P0_R7_D[7:6]) register bits. As shown in Table 7-2 and Table 7-3, these modes are all most significant byte

(MSB)-first, pulse code modulation (PCM) data format, with the output channel data word-length programmable

as 16, 20, 24, or 32 bits by configuring the ASI_WLEN[1:0] (P0_R7_D[5:4]) register bits.

Table 7-2. Audio Serial Interface Format

P0_R7_D[7:6] : ASI_FORMAT[1:0] AUDIO SERIAL INTERFACE FORMAT

00 (default) Time division multiplexing (TDM) mode

01 Inter IC sound (I

2

S) mode

10 Left-justified (LJ) mode

11 Reserved (do not use this setting)

Table 7-3. Audio Output Channel Data Word-Length

P0_R7_D[5:4] : ASI_WLEN[1:0] AUDIO OUTPUT CHANNEL DATA WORD-LENGTH

00 Output channel data word-length set to 16 bits

01 Output channel data word-length set to 20 bits

10 Output channel data word-length set to 24 bits

11 (default) Output channel data word-length set to 32 bits

The frame sync pin, FSYNC, is used in this audio bus protocol to define the beginning of a frame and has the

same frequency as the output data sample rates. The bit clock pin, BCLK, is used to clock out the digital audio

data across the serial bus. The number of bit-clock cycles in a frame must accommodate multiple device active

output channels with the programmed data word length.

A frame consists of multiple time-division channel slots (up to 64) to allow all output channel audio data

transmissions to complete on the audio bus by a device or PCMD3140-Q1 and other Audio devices sharing the

same bus. The device supports up to four output channels that can be configured to place their audio data on

bus slot 0 to slot 63. Table 7-4 lists the output channel slot configuration settings. In I

2

S and LJ mode, the slots

are divided into two sets, left-channel slots and right-channel slots, as described in the Section 7.3.1.2.2 and

Section 7.3.1.2.3 sections.

Table 7-4. Output Channel Slot Assignment Settings

P0_R11_D[5:0] : CH1_SLOT[5:0] OUTPUT CHANNEL 1 SLOT ASSIGNMENT

00 0000 = 0d (default) Slot 0 for TDM or left slot 0 for I

2

S, LJ.

00 0001 = 1d Slot 1 for TDM or left slot 1 for I

2

S, LJ.

… …

01 1111 = 31d Slot 31 for TDM or left slot 31 for I

2

S, LJ.

10 0000 = 32d Slot 32 for TDM or right slot 0 for I

2

S, LJ.

… …

11 1110 = 62d Slot 62 for TDM or right slot 30 for I

2

S, LJ.

11 1111 = 63d Slot 63 for TDM or right slot 31 for I

2

S, LJ.

Similarly, the slot assignment setting for output channel 2 to channel 4 can be done using the CH2_SLOT

(P0_R12) to CH8_SLOT (P0_R18) registers, respectively.

The slot word length is the same as the output channel data word length set for the device. The output channel

data word length must be set to the same value for all PCMD3140-Q1 devices if all devices share the same ASI

bus in a system. The maximum number of slots possible for the ASI bus in a system is limited by the available

bus bandwidth, which depends upon the BCLK frequency, output data sample rate used, and the channel data

word length configured.

www.ti.com

PCMD3140-Q1

SBASAH3 – APRIL 2022

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

17

Product Folder Links: PCMD3140-Q1