US5D310:2.1GHz高性能差分时钟缓冲器规格

需积分: 38 104 浏览量

更新于2024-08-04

1

收藏 1.48MB PDF 举报

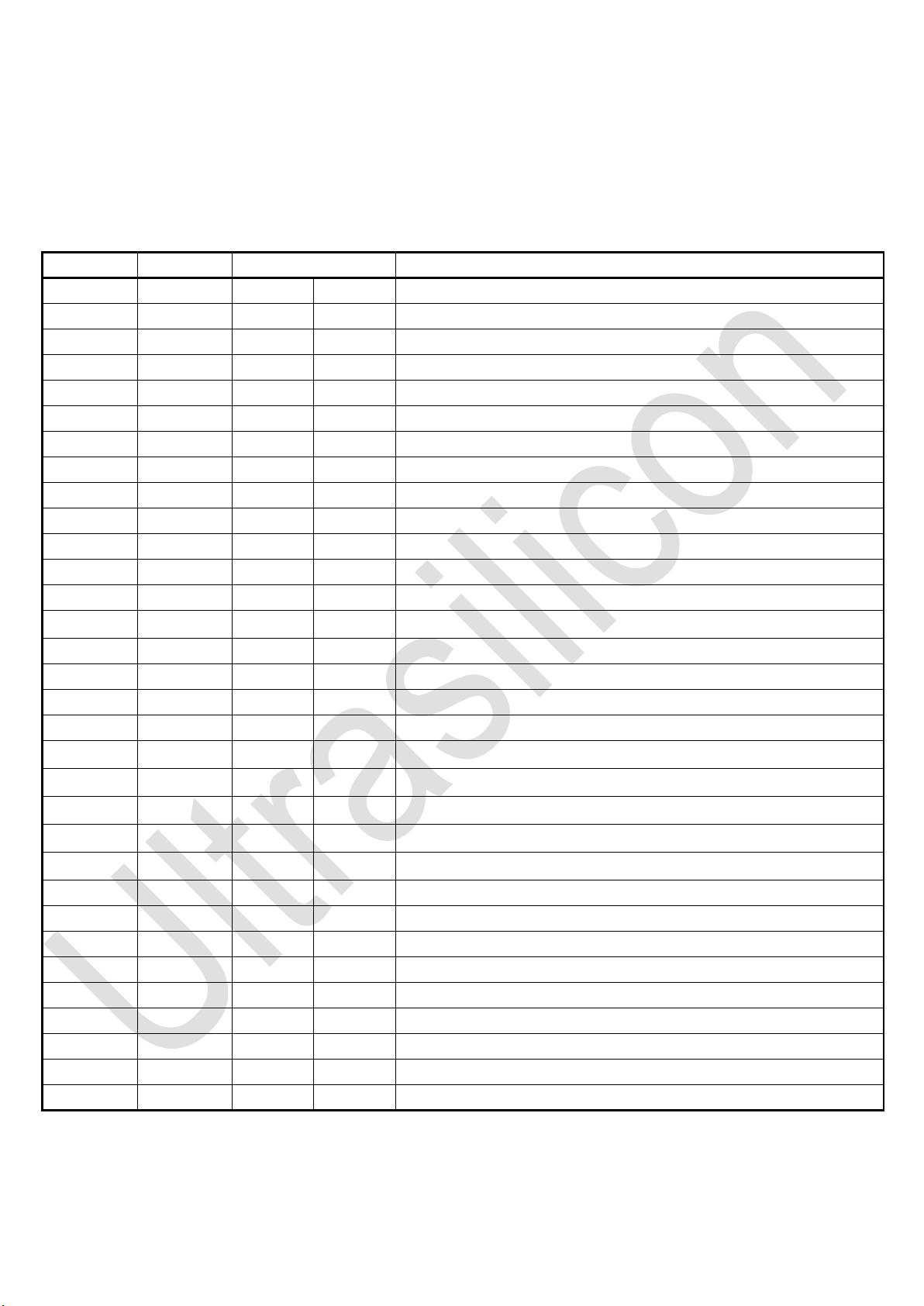

US5D310是一款高性能的差分时钟缓冲器,专为满足2.1GHz高速应用设计,具备2组10路独立配置的差分输出。这款产品支持多种电平标准,包括LVPECL、LVDS和HSCL,旨在提供低抖动特性,适合对时钟质量要求极高的环境,如高频通信系统、数据中心基础设施和医疗设备中的信号传输。

US5D310的关键特性包括:

1. 高精度时钟输出:通过附加抖动控制在10kHz到20MHz频率范围内的性能为50fs,确保了输出时钟的稳定性。输出间的偏斜误差保持在10ps,而器件间的最大偏斜仅为30ps,这对于信号同步至关重要。

2. 灵活输入选项:允许三种输入信号选择,包括差分LVPECL、LVDS、HSTL的AC/DC信号,以及单端LVCMOS/LVTTL/HSTL输入。内置的晶振电路支持10-200MHz频率范围,集成度高且能有效降低100MHz晶体的频率积分抖动至70fs。

3. 低功耗设计:作为一款低功耗解决方案,US5D310在提供高效性能的同时,注重能源效率,适合移动和便携式设备的应用场景。

4. 小型封装:采用紧凑的32-pin 5x5 QFN封装,占用空间小,便于集成到各种板卡设计中。

5. 非法输入处理:当输入信号不合法时,US5D310能够自动进入预定义状态,保证系统的鲁棒性。

6. 易于配置:通过简单的pin编程,用户可以快速调整核心电压和输出电压,以适应不同的系统需求。

此款国产时钟芯片US5D310广泛应用于无线和有线网络基础设施、数据通信、医学成像、便携式测试测量设备以及高端音频/视频系统,其出色的性能和灵活性使其成为这些领域中实现低抖动时钟信号传输的理想选择。若需进一步的技术支持或购买信息,可联系销售邮箱sales@ultrasilicon.com.cn。

2021-06-08 上传

2021-07-16 上传

2023-06-07 上传

2023-06-07 上传

2023-06-07 上传

2023-06-07 上传

2023-06-07 上传

2023-08-07 上传

时钟芯片

- 粉丝: 18

- 资源: 3

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录