使用Designer's Timer进行静态时序分析

需积分: 10 51 浏览量

更新于2024-07-30

收藏 680KB PDF 举报

"静态时序分析是集成电路设计后端的关键步骤,主要介绍Actel公司的Designer's Timer工具在静态时序分析中的应用,包括预布局和后布局分析以及约束设置。"

在数字集成电路设计中,静态时序分析(Static Timing Analysis, STA)是一个至关重要的环节,它用于评估设计的性能并确保其满足预定的时序要求。静态时序分析比基于激励向量的门级仿真更快,不需要生成刺激向量。因此,它的效率不依赖于刺激向量的质量。然而,静态分析无法验证设计的正确功能,只能确保设计的时序特性。

Actel公司的Designer's Timer是一款集成在Designers软件中的静态时序分析工具,它可以进行预布局和后布局的分析,帮助设计者设置和管理设计的时序约束。预布局分析在逻辑综合之后进行,主要用于评估基本的逻辑结构和时序;而后布局分析则是在物理布局完成后,考虑了实际的布线延迟,提供更为精确的时序信息。

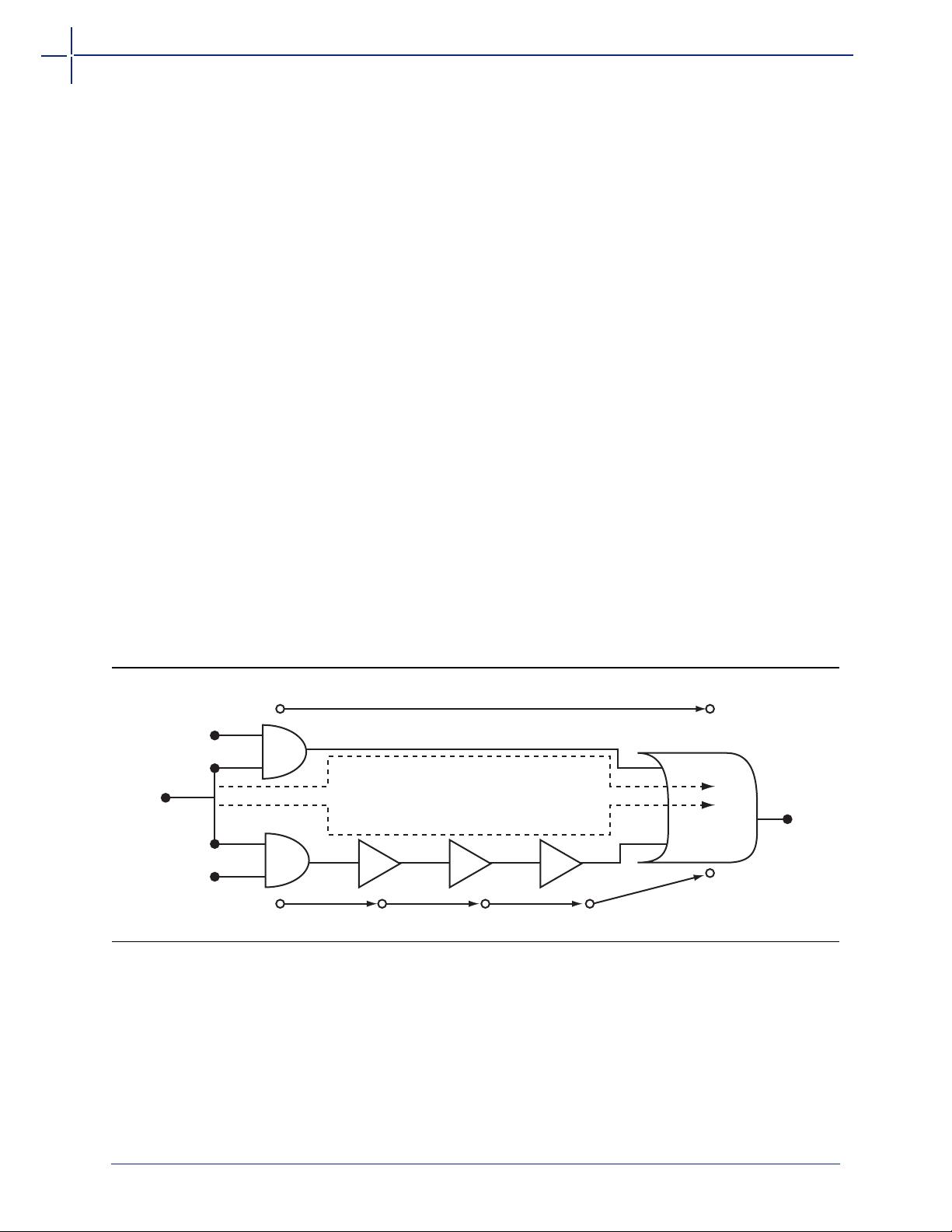

静态时序分析的核心概念包括路径延迟、时钟周期、建立时间(Setup Time)和保持时间(Hold Time)。路径延迟是指信号从源触发器到目的地触发器通过逻辑门传播所经历的时间。时钟周期定义为系统最慢路径的延迟,是设计的时钟速率的决定因素。建立时间和保持时间是确保数字电路在时钟边沿正确工作的关键,前者规定数据必须在时钟上升沿之前稳定,后者规定数据在时钟上升沿之后保持稳定。

Designer's Timer提供了以下关键功能:

1. **路径分析**:找出设计中最慢的路径,即关键路径,以优化设计性能。

2. **时钟树合成**:构建时钟树模型,准确地模拟时钟信号的传播延迟。

3. **约束管理**:允许用户设定各种时序约束,如最大时钟周期、最小建立时间和保持时间等。

4. **报告生成**:生成详细的时序报告,包括路径延迟、时钟域交叉问题等信息。

5. **优化建议**:根据分析结果给出改进设计时序的建议。

通过实践例子,应用笔记深入讲解如何使用Designer's Timer进行静态时序分析,包括如何设置和解决常见的时序问题,如时钟偏移、时钟抖动、路径瓶颈等。掌握这些概念和技术,可以显著提高设计性能,简化设计调试流程,缩短产品开发周期。

静态时序分析是数字集成电路设计中不可或缺的工具,它帮助设计者在设计阶段就能预测和优化电路的时序性能,确保设计在实际运行时满足严格的时序要求。Actel的Designer's Timer为此提供了强大的支持,通过理解和应用该工具,设计师能够更高效地管理和提升设计的时序特性。

2021-10-02 上传

2022-06-14 上传

2020-06-11 上传

2023-03-16 上传

2010-03-25 上传

2017-12-03 上传

2024-01-15 上传

2023-03-16 上传

2019-05-23 上传

miya_wangli

- 粉丝: 0

- 资源: 1

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器