Nios处理器的FPGA硬件开发详解

需积分: 0 15 浏览量

更新于2024-07-28

收藏 932KB PDF 举报

"第四章FPGA硬件开发主要讲解了Nios处理器的硬件开发环境和流程,涉及Nios开发系统组成,SOPC Builder的使用,Quartus II软件的集成,以及硬件编译和编程过程。"

在FPGA硬件开发中,Nios处理器是一个关键组件,它是一种可定制的、嵌入式的软核处理器,常用于实现复杂的数字逻辑功能。Nios开发系统由Nios嵌入式处理器和与其连接的外设输入输出设备构成。硬件开发流程主要包括以下几个步骤:

1. **系统开发流程概述**:

- 系统需求分析:确定系统计算性能需求、位宽和吞吐量,以及定制特定的CPU功能,如是否需要硬件乘法器,需要哪些外设,是否需要DMA通道等。

- 硬件设计:使用SOPC Builder整合处理器和接口控制器,创建定制的硬件系统。

- 软件设计:编写与硬件平台无关的C/C++代码。

- 集成与测试:硬件和软件的交互,确保两者协同工作。

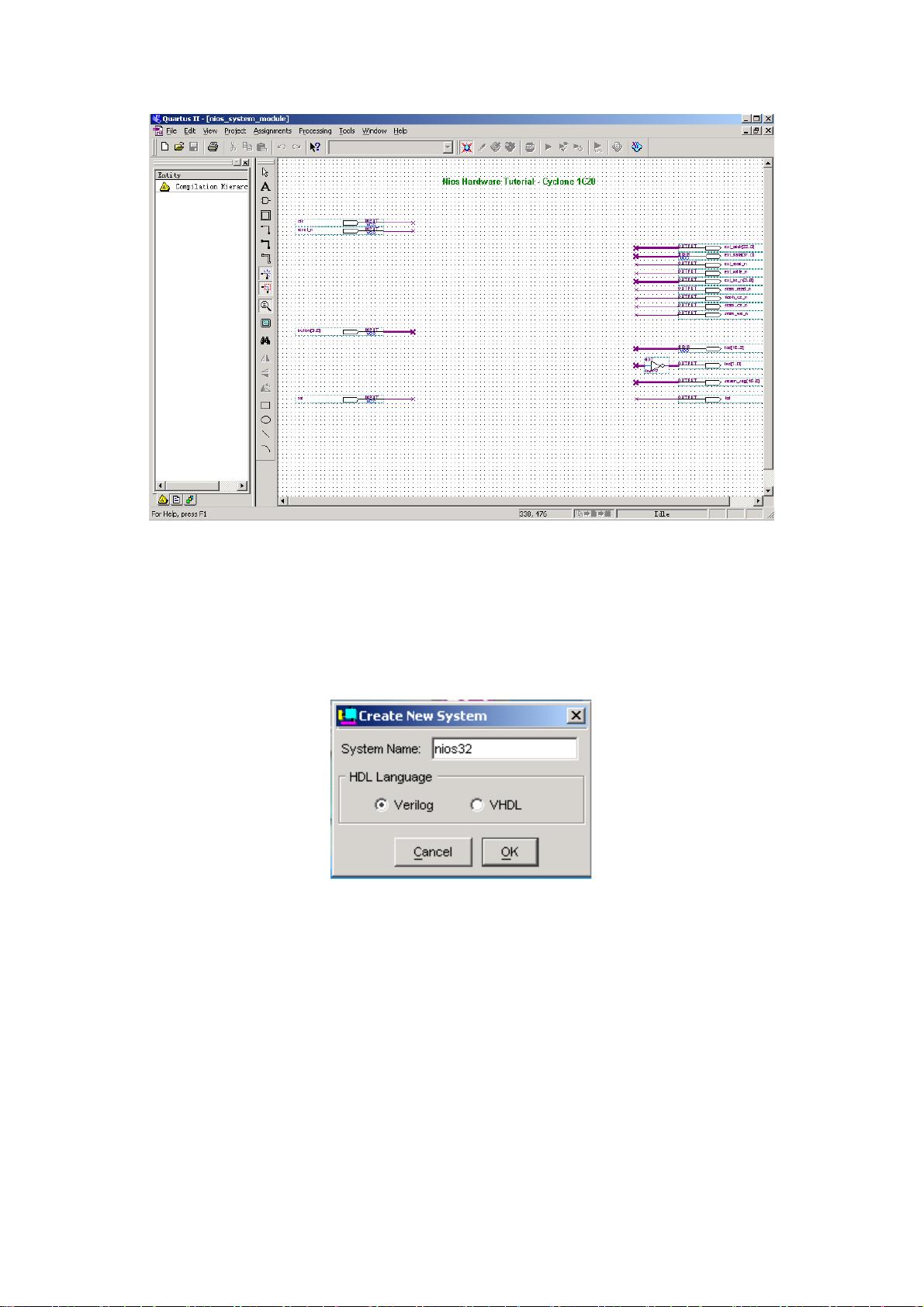

2. **进入Quartus II工程**:

- 使用Quartus II作为主要的FPGA设计和编译工具,这是Altera公司的综合开发平台,支持多种硬件描述语言和设计流程。

3. **创建Nios系统模块**:

- 启动SOPC Builder,这是一个图形化工具,用于配置和生成Nios处理器及外设的系统模块。

- 设定系统主频:根据设计需求设置处理器的工作频率。

- 加入CPU和外设:选择需要的处理器类型和其他外设,如GPIO、UART、SPI等。

- 设定基址:为每个外设分配地址空间,确保它们在内存映射中不冲突。

- 生成系统模块:SOPC Builder根据配置自动生成硬件描述文件。

- BDF文件中加入系统模块:将生成的系统模块整合进 Quartus II 的工程文件中。

4. **编译系统模块**:

- 在Quartus II中编译整个系统模块,完成逻辑综合和布局布线,优化逻辑资源的使用。

5. **编程(Programming)**:

- 配置FPGA:将编译后的配置文件下载到FPGA中,实现硬件逻辑。

- 下载配置到flash存储器:为了实现系统上电自启动,通常会将配置文件烧录到板载的非易失性存储器中。

整个流程中,硬件和软件开发相互交织,SDK(Software Development Kit)是两者之间的桥梁,确保硬件平台和软件应用的兼容性。无论是独立开发还是团队协作,理解整个硬件和软件开发流程都是至关重要的,这有助于构建出高效、稳定且符合预期的嵌入式系统。

129 浏览量

377 浏览量

249 浏览量

183 浏览量

161 浏览量

217 浏览量

233 浏览量

170 浏览量

175 浏览量

ligang411

- 粉丝: 0

最新资源

- ODI安装配置教程:文档与工具指南

- C语言函数速查手册:常用函数全掌握

- Andorid开发系列课程-Day03视频

- 深入理解UIAlertController在iOS8.0中的应用

- Gradle Android插件的开源压缩包介绍

- Java拉博训练教程与项目实战

- 得意奶茶销售管理系统:提升销售效率与管理

- 传智播客Android课程北京站Day02视频教程

- 2009新年快乐PPT模板下载

- 微信小程序前端打卡功能开发教程

- 基于SpringMVC3.2和jQuery1.9的Restful入门实践

- 掌握网格断点技术-crx插件使用攻略

- 深入解析PigDev-master压缩包子文件的开发

- shake.js的使用方法及事件处理实现

- Andorid智慧北京Day01课程视频解析

- 西门子SITRANS LG270探针操作与维护指南