优化的二进制加法器设计:半加器与全加器原理

需积分: 15 51 浏览量

更新于2024-08-06

收藏 195KB PDF 举报

反相加法器原理图与电路图资料是一份关于数字逻辑设计中的基础组件介绍,主要针对电子工程师和计算机科学家。加法器作为最基本的算术运算单元,其核心是实现数字信号的相加。加法器根据功能可分为两类:半加器和全加器。

半加器是加法器的基本单元,它接受两个二进制位(A和B)作为输入,通过异或(XOR)操作得到和(S),同时通过与(AND)操作确定进位(C)。半加器只能处理单个位的加法,无法处理进位问题。

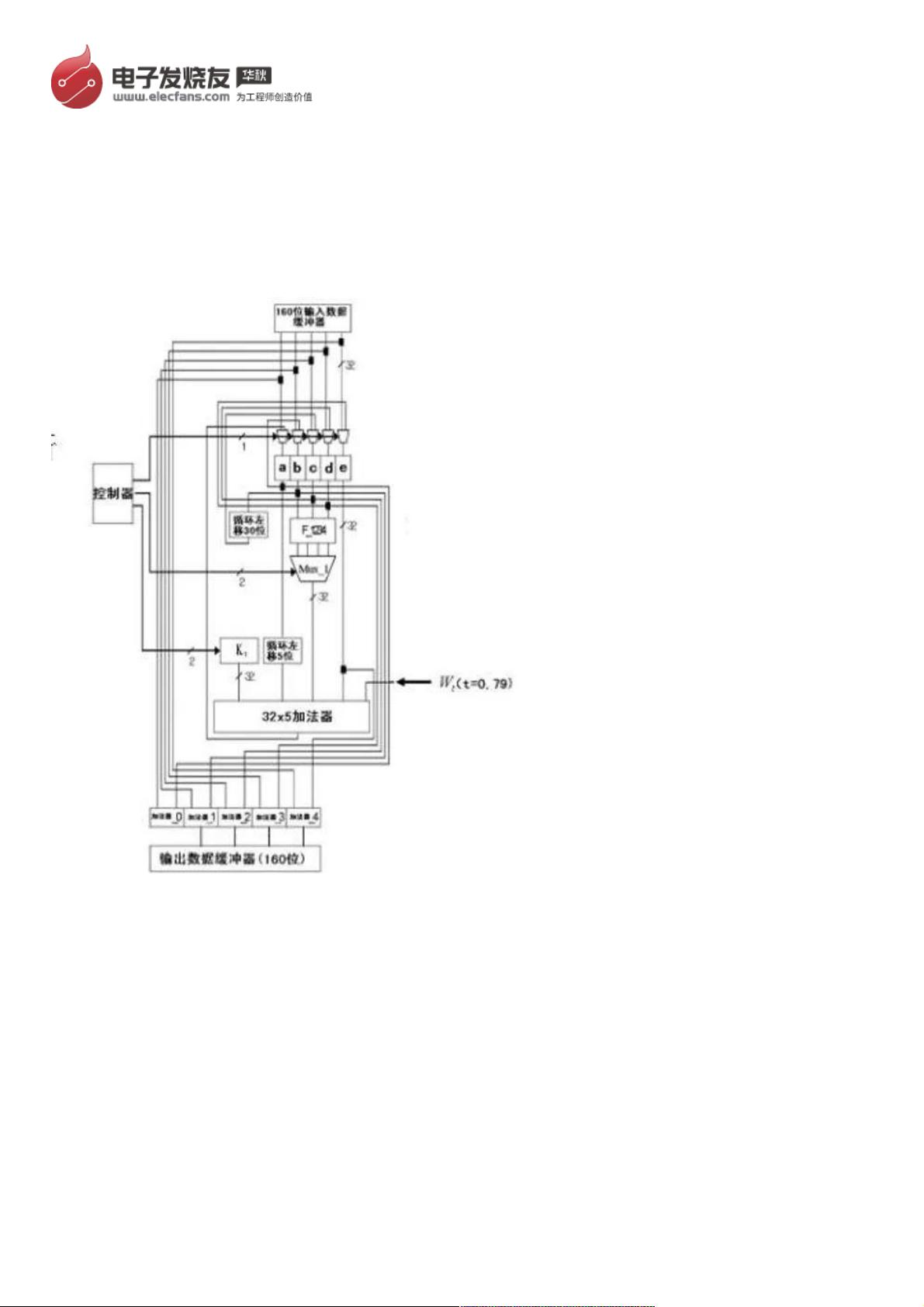

全加器在此基础上增加了对进位的处理能力,它除了接收A和B外,还有一个额外的进位输入(Ci或Cin)。全加器通过两个半加器的组合实现,不仅能完成当前位的加法,还能处理来自低位的进位。它的输出包括和S以及新的进位Cout。全加器的电路设计更为复杂,但效率更高,适用于多位数的加法,如在计算机中处理32位二进制数的加法时,全加器的并行结构能够显著缩短计算时间。

实现多位数的加法,通常采用逐位进位的方法,即通过级联多个全加器,将低位的和和进位传递给高位。然而,这种方法会导致加法过程时间线性增加。为了提高速度,可以通过设计并行结构或者流水线技术,让不同位的加法可以同时进行,从而实现加法的并行化。

反相加法器原理图与电路图资料不仅介绍了基本的加法器概念,还深入探讨了如何通过半加器和全加器构建高效的多位加法器,这对于理解和设计现代计算机内部的算术逻辑部件至关重要。学习和掌握这些原理,对于从事硬件设计、嵌入式系统开发或数字信号处理等领域的工作人员来说,都是非常重要的基础知识。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2023-08-03 上传

2021-06-01 上传

2021-09-02 上传

2020-07-27 上传

2021-02-03 上传

weixin_38732842

- 粉丝: 4

- 资源: 951

最新资源

- HPUX 11i V3系统管理员指南

- DIV+CSS布局大全

- J2EE 设计开发编程

- Serial ATA 2.6 Specification

- ITIL-white

- 《LINUX与UNIX SHELL编程指南》读书笔记

- 单源最短路径问题的Dijkstra算法

- Oracle 10g R2 Concepts双语版

- 02 第四章 使用SQL语句.pdf

- spring2.5 reference

- API函数大全(32 Bit Section PowerBuilder API)

- 51汇编指令表,一目了然,希望大家多多交流学习

- Serial ATA Specification Rev. 2.5

- 01 第一~三章.pdf

- asp.net速成教程

- Understanding JTA