Allegro约束规则设置指南V1.2:线宽、间距与走线长度

需积分: 19 147 浏览量

更新于2024-08-02

收藏 735KB PDF 举报

"Allegro中的约束规则设置V1.2.pdf"

Allegro是一款广泛应用于PCB设计的专业软件,其强大的约束规则设置是保证电路板设计质量的关键环节。本资料详细介绍了Allegro中关于物理特性(线宽和过孔)、间距、区域以及走线长度的约束规则设置,确保设计符合规范,提高设计效率。

一、Physical(Line/vias)rule 物理特性(线宽和过孔)约束设置:

1) “Set values”设置约束特征值:这一部分允许用户设定电路板上导线和过孔的最小、最大宽度,以及特定层的特定宽度。通过这个功能,设计师可以确保线路的电气安全性和机械稳定性,避免短路和断裂的风险。

2) “Attach property”绑定约束:此功能允许将特定的线宽和过孔约束规则与电路板上的特定对象关联起来,例如元件、网络或者特定区域,实现定制化的约束管理。

3) “Assignment table”约束规则分配:在这个表格中,设计师可以批量分配约束规则,节省时间并确保一致性,同时可以根据不同的设计需求灵活调整规则。

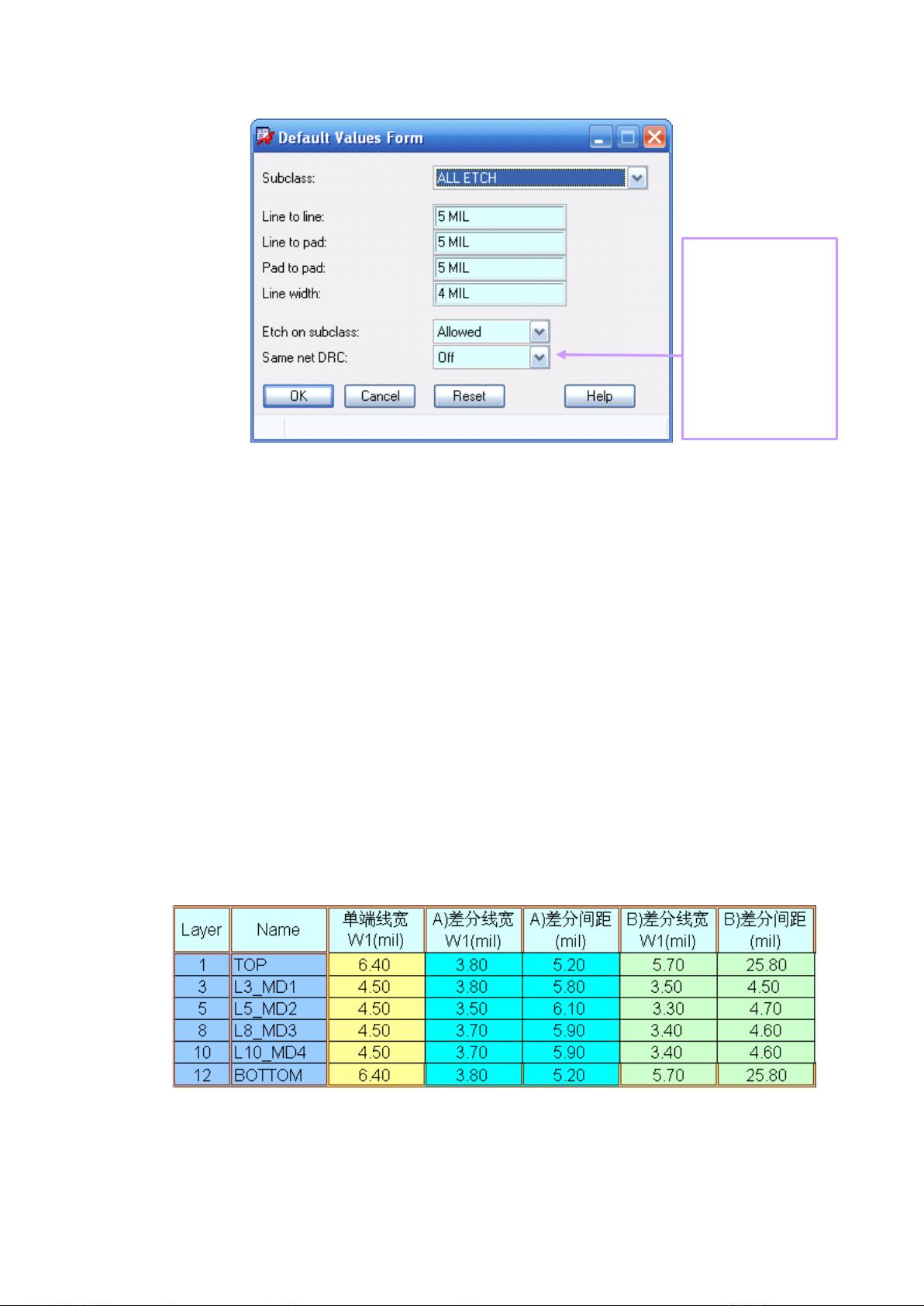

二、“Spacing rule”间距约束设置:

1) “Set values”设置约束特征值:同样用于定义电路板上不同对象间的最小安全距离,如导线与导线、导线与过孔、过孔与过孔之间的间距,以防止潜在的电气干扰和短路。

2) “Attach property”绑定约束:将特定的间距约束规则应用到特定对象,确保设计的精确性和合规性。

3) “Assignment table”约束规则分配:类似于物理特性的分配,此功能用于批量设定间距规则,便于管理和优化设计。

三、Constraint areas 区域约束设置:

区域约束允许设计师对电路板的特定区域设定特定的规则。比如,可以设定高密度区的线宽和间距要求不同于低密度区,以适应不同功能区域的需要。这有助于优化布线,减少电磁干扰,提高信号完整性和电源完整性。

四、Allegro中走线长度的设置:

1) 差分线等长设置:对于高速数字设计,差分对的等长至关重要,因为它直接影响信号的质量。设计师可以设定一对差分线的长度差异限制,以确保信号的同步传输。

2) 一组Net等长:一组网络的所有导线应保持等长,以保证信号的同步,减少时序问题。可以通过工具快速调整一组Net的长度,使其达到一致。

3) XNet等长:XNet等长是指多个不相关的Net也保持等长,以优化整体信号的传播延迟,提高系统性能。

通过这些详尽的约束规则设置,设计师可以在Allegro中实现精细化的设计控制,确保电路板设计的质量和可靠性。同时,Allegro提供的直观界面和灵活的规则分配方法使得复杂的设计任务变得更为易管理和高效。

2023-05-19 上传

2021-10-19 上传

124 浏览量

2021-11-01 上传

2022-11-04 上传

2020-12-18 上传

点击了解资源详情

wjq5588

- 粉丝: 0

- 资源: 27

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程