VHDL实现的数字时钟设计与分析

版权申诉

77 浏览量

更新于2024-06-25

收藏 534KB DOC 举报

该文档是关于基于VHDL的数字时钟设计的详细报告,涵盖了设计原理、系统架构、模块实现、仿真与调试等环节。

1. 数字时钟工作原理

数字时钟的核心组成部分包括秒计数器、分计数器和小时计数器,它们都是基于60进制(秒、分)和24进制(小时)的计数器。时钟电路通过接收1Hz的计数脉冲(通常由50MHz晶振分频得到)来更新秒数,秒计数器的进位信号驱动分计数器,分计数器的进位信号再驱动小时计数器。每当达到23小时59分59秒时,时钟会重置并重新开始计时。此外,系统中还有一个CPU(如NIOS),它响应秒计数器的中断信号,读取并解码当前时间,然后在七段数码管上显示。

1. 设计任务

设计目标是构建一个VHDL实现的数字时钟,具备以下功能:

- 在七段数码管上实时显示时、分、秒。

- 实现24小时制,且分、秒按照60进制计数,小时满24进1。

- 整点报时,即到达整小时时,扬声器发出提示音。

- 时间设置功能,通过按键调整秒和分,支持清零和暂停操作。

- LED灯循环显示,时钟运行时,LED依次亮起。

2. 系统总体方案设计

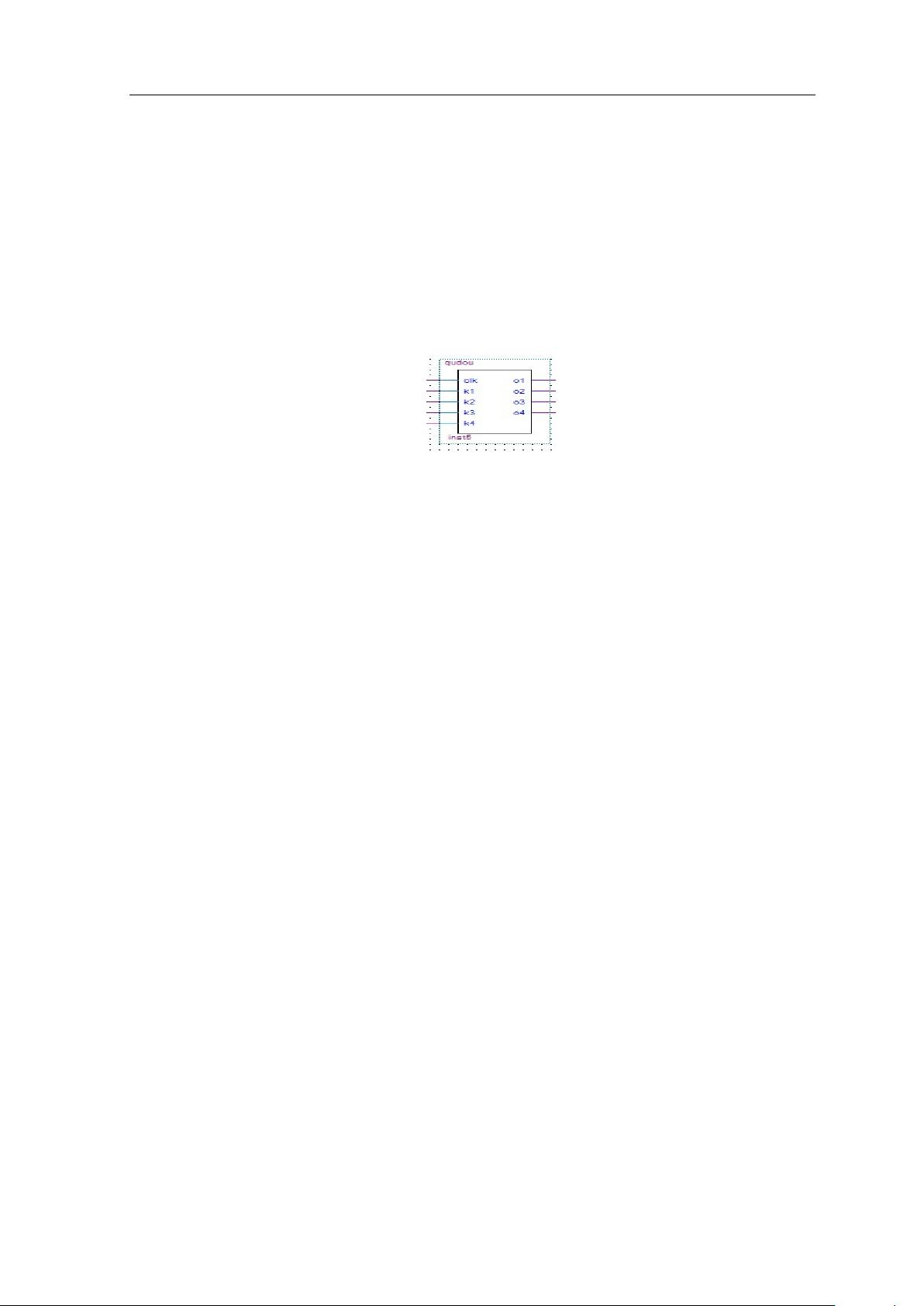

采用自顶向下的模块化设计方法,包括7个底层模块:秒计数器、分计数器、时计数器、按键去抖动模块、按键控制模块、时钟分频模块和数码管显示模块。顶层设计以原理图形式集成这些模块。设计框图描绘了各模块间的连接关系,50MHz系统时钟经过分频产生1秒信号,作为秒计数器的输入,进而驱动其他计数器和系统功能。

3. VHDL模块电路设计

- 分频模块:将50MHz系统时钟转换为1Hz的计时信号。

- 按键去抖动模块:处理按键输入,消除因机械抖动造成的误触发。

- 按键控制模块:根据按键状态控制计数器的增减或暂停。

- 分六十进制模块:处理秒和分的60进制计数逻辑。

- 时计数模块:实现24小时制的计数。

- 组合模块:将秒、分、时的计数结果组合起来。

- 数码管显示模块:将时间数据转换为七段数码管的显示信号。

4. 系统仿真与调试

在设计完成后,需要进行系统仿真以验证各个模块的正确性,确保时钟能够准确计时、正确显示,并响应按键操作。调试阶段可能需要修正逻辑错误,优化性能,确保系统稳定可靠。

5. 结束语与致谢

文档最后总结了设计过程和经验,列出参考文献,并表达了对指导老师和协助者的感谢。

6. 附录

附录包含了源代码,供读者查阅和学习VHDL编程技巧。

这份文档提供了基于VHDL的数字时钟设计的完整流程,从理论到实践,展示了硬件描述语言在数字系统设计中的应用。

258 浏览量

109 浏览量

2024-11-07 上传

2024-11-07 上传

2024-11-07 上传

2024-11-08 上传

2024-11-08 上传

133 浏览量

老帽爬新坡

- 粉丝: 99

最新资源

- Java实现推箱子小程序技术解析

- Hopp Doc Gen CLI:打造HTTPS API文档利器

- 掌握Pentaho Kettle解决方案与代码实践

- 教育机器人大赛51组代码展示自主算法

- 初学者指南:Android拨号器应用开发教程

- 必胜客美食宣传广告的精致FLASH源码解析

- 全技术领域资源覆盖的在线食品商城购物网站源码

- 一键式FTP部署Flutter Web应用工具发布

- macOS下安装nVidia驱动的简易教程

- EGOTableViewPullRefresh: GitHub热门下拉刷新Demo介绍

- MMM-ModuleScheduler模块:MagicMirror的显示与通知调度工具

- 哈工大单片机课程上机实验代码完整版

- 1000W逆变器PCB与原理图设计制作教程

- DIV+CSS3打造的炫彩照片墙与动画效果

- 计算机网络基础与应用:微课版实训教程

- gvim73_46:最新GVIM编辑器的发布与应用