FPGA多分辨率图像采集系统:实时预处理与压缩性能提升

41 浏览量

更新于2024-08-30

收藏 341KB PDF 举报

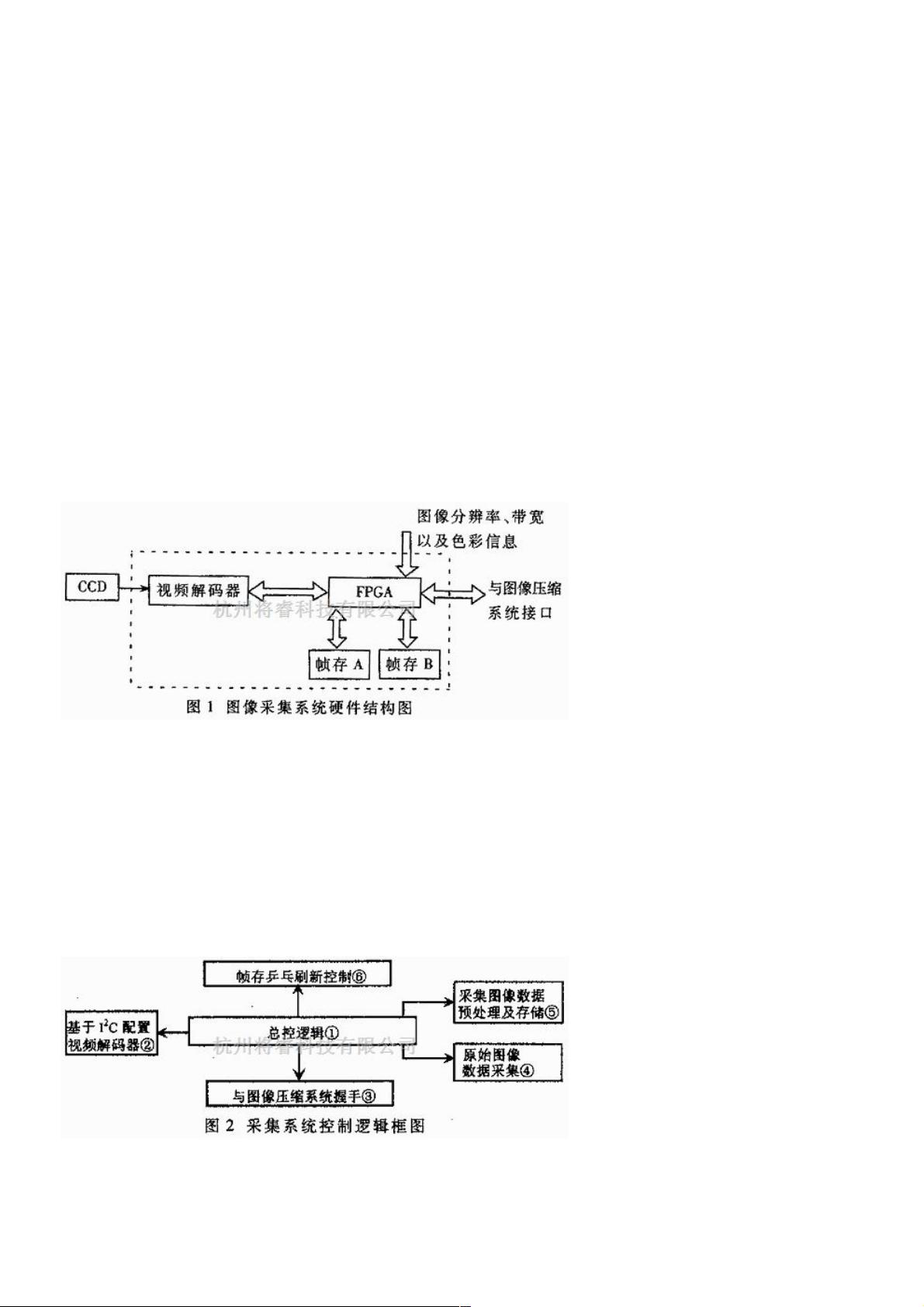

在现代数字多媒体技术背景下,多分辨率图像实时采集系统的FPGA逻辑设计成为关键环节。该研究论文提出了一种创新的FPGA架构,用于构建实时且具有灵活性的图像采集系统。系统的核心在于控制逻辑设计,特别是图像数据预处理和帧存乒乓刷新机制,这两者直接影响到系统性能和数据传输效率。

图像数据预处理是系统的第一道防线,它通过高效的算法对原始图像进行初步处理,如噪声过滤、色彩校正等,降低后续处理的复杂性和计算负担。预处理部分的FPGA设计需考虑硬件并行性和资源优化,以实现实时性要求。

帧存乒乓刷新机制则是确保连续图像流的关键,通过周期性地在高速缓存(Frame Buffer)和外存之间切换存储位置,避免了数据冗余和带宽瓶颈,提高了数据传输的流畅性。这种机制的设计与FPGA的流水线操作和内存管理密切相关,对时序控制和硬件资源调度有很高的要求。

论文作者通过对比实验,验证了他们设计的图像采集系统在图像压缩系统中的作用。实验结果显示,新的图像采集系统不仅稳定性强,而且显著提升了整个图像处理系统的性能,尤其是在高帧率和高分辨率的场景下,相比于传统视频压缩芯片、专用信号处理器或通用DSP,FPGA的定制化设计能够提供更高效的数据处理能力。

在设计过程中,论文重点介绍了如何在中央控制器的协调下,利用FPGA的并行处理能力,同时处理多个图像数据流,以满足并行处理的性能需求。这种方法有效地解决了数据量庞大的问题,使得图像处理系统能够在保证实时性和效率的同时,应对日益增长的图像处理需求。

本文通过深入探讨FPGA在多分辨率图像实时采集系统中的应用,展示了其在控制逻辑设计、图像预处理和系统整合方面的优势,为实际的数字图像处理系统提供了新的设计思路和实践案例。这对于推动数字多媒体技术的发展,特别是提高图像处理系统的性能和响应速度具有重要意义。

2020-11-07 上传

2020-12-09 上传

2020-11-11 上传

2023-08-25 上传

2024-06-30 上传

2024-11-11 上传

2024-11-11 上传

2023-10-29 上传

2023-08-18 上传

weixin_38699613

- 粉丝: 2

- 资源: 923

最新资源

- mp3-文件-

- mR-zUnnu

- C#-Leetcode编程题解之第22题括号生成.zip

- jquery打分评星级效果

- bootstrap-wysiwyg-notes:简易富文本编辑器bootstrap-wysiwyg原始注解,可用于学习富文本实现原理

- Mutilsim 设计一个串行数据检测电路. 当连续出现4个和4个以上的1时, 检测输出信号为1, 其余情况下的输出信号为0

- online-vet-clinic:基于Spring宠物诊所项目的在线兽医诊所

- hyperdrive-network-speed:跟踪Hyperdrive存档上的上传和下载速度

- git-github的

- original

- 5953281,c语言源码反码补码转换,c语言

- uniapp + vue3 +vite + ts + pinia 框架模板

- LeisureConstructionWebsite:leisureconstruction.com PHPSlim Restful网站源代码-Source website php

- Python库 | sqla_inspect-0.1.6.tar.gz

- 练习:练习会使您的大脑融化

- 蓝色手机APP应用开发网站模板