USB2.0控制器CY7C68013与FPGA接口Verilog HDL实现

需积分: 0 89 浏览量

更新于2024-08-05

收藏 185KB PDF 举报

该文介绍了如何使用Verilog HDL实现USB 2.0控制器CY7C68013与FPGA之间的接口设计,重点在于利用控制器的Slave FIFO模式进行高速数据传输。该系统适用于各种需要高速数据传输的场景,如数据采集或硬盘控制。

正文:

USB 2.0控制器CY7C68013是一款广泛应用的设备,因其高效的数据传输速度和灵活的接口方式而受到青睐。该控制器支持低速(1.5 Mbit/s)、全速(12 Mbit/s)和高速(480 Mbit/s)三种模式,满足了大多数外设接口的需求。文章主要关注高速模式下的应用,尤其是在与FPGA结合时的数据传输优化。

FPGA(现场可编程门阵列)是一种可编程的集成电路,能够根据设计需求灵活配置逻辑电路。通过Verilog HDL(硬件描述语言),设计者可以定义FPGA中的逻辑行为,实现特定的控制逻辑和数据处理任务。

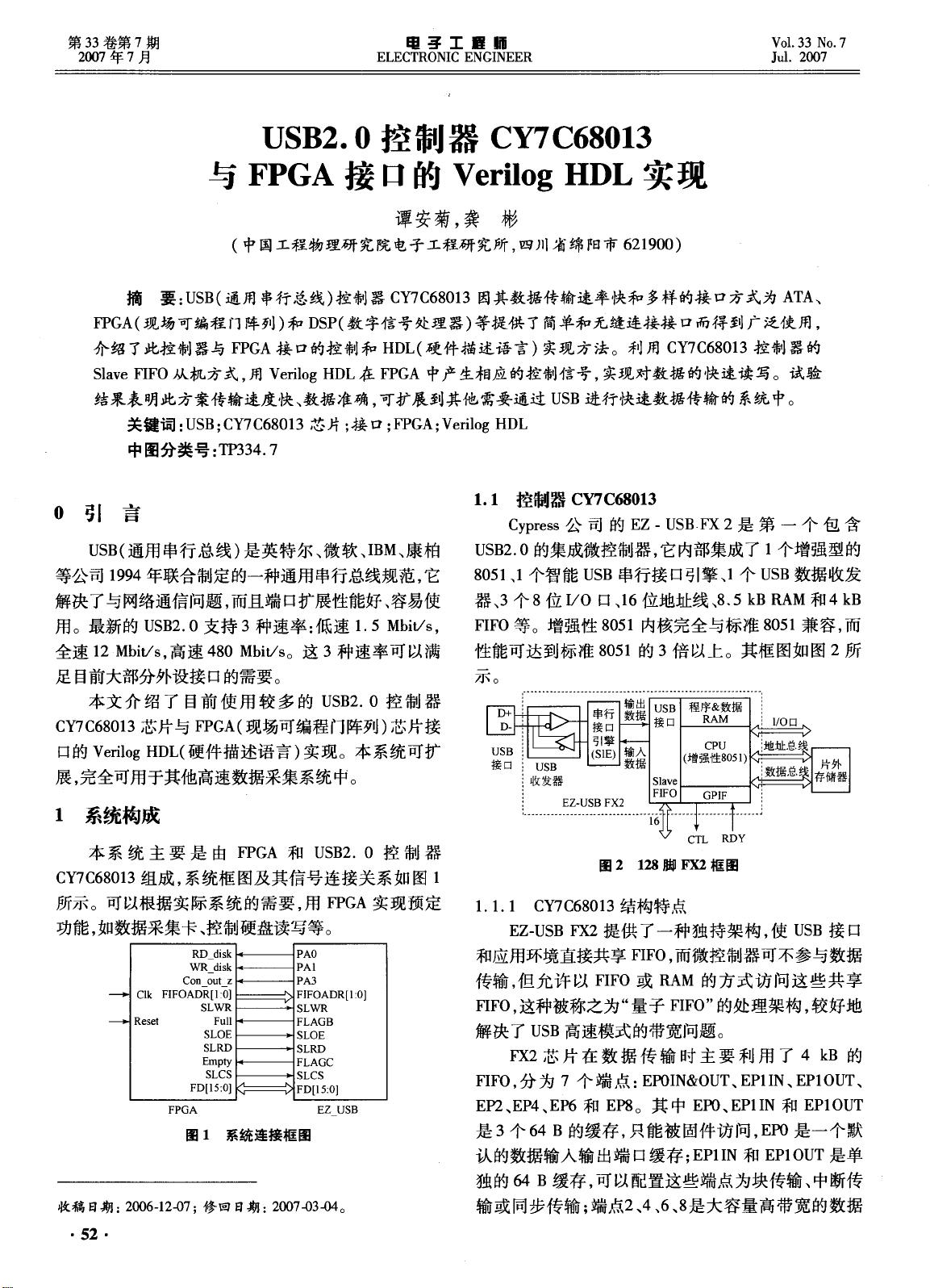

在本文中,CY7C68013被配置为Slave FIFO模式,这是一种从机模式,允许FPGA作为主设备来控制数据的读写操作。Slave FIFO模式下,CY7C68013提供了Full和Empty标志,用于指示缓冲区的状态,帮助FPGA准确地控制数据流。FPGA通过这些信号生成读写控制信号SLRD和SLWR,以及片选信号SLCS,来与CY7C68013进行同步通信。

接口设计的关键在于Verilog HDL的实现,这包括了对控制信号的生成、数据传输路径的建立以及错误处理机制。Verilog HDL使得设计者可以清晰地描述硬件逻辑,简化了接口设计的复杂性,并且可以进行仿真验证,确保设计的正确性。

在系统框图中,我们可以看到FPGA与CY7C68013之间的信号连接关系,包括地址线(FIFOADR[1:0])、数据线(FD[15:0])、读写控制线(SLRD, SLWR)以及状态标志线(Full, Empty)。FPGA通过这些连接控制数据的读写,同时监控缓冲区的状态,确保数据传输的高效和无误。

通过这种接口设计,系统可以实现快速的数据交换,且具有良好的扩展性。实验结果表明,该方案在数据传输速度和准确性上表现优秀,适用于需要高速USB接口的系统,如数据采集卡或硬盘控制等应用。由于采用Verilog HDL,设计的复用性和可移植性也得到了保障,使得该方案可以轻易地应用于其他类似需求的项目。

总结,本文详细阐述了如何使用Verilog HDL实现USB 2.0控制器CY7C68013与FPGA之间的高效接口设计,这一设计方法对于需要高速数据传输的系统开发具有重要的参考价值。通过这种设计,可以构建出稳定、快速的USB通信系统,满足现代电子设备对高速数据交换的需求。

点击了解资源详情

点击了解资源详情

176 浏览量

260 浏览量

251 浏览量

214 浏览量

2022-07-14 上传

2022-07-15 上传

永远的12

- 粉丝: 1115

最新资源

- 小学水墨风学校网站模板设计

- 深入理解线程池的实现原理与应用

- MSP430编程代码集锦:实用例程源码分享

- 绿色大图幻灯商务响应式企业网站开发源码包

- 深入理解CSS与Web标准的专业解决方案

- Qt/C++集成Google拼音输入法演示Demo

- Apache Hive 0.13.1 版本安装包详解

- 百度地图范围标注技术及应用

- 打造个性化的Windows 8锁屏体验

- Atlantis移动应用开发深度解析

- ASP.NET实验教程:源代码详细解析与实践

- 2012年工业观察杂志完整版

- 全国综合缴费营业厅系统11.5:一站式缴费与运营管理解决方案

- JAVA原生实现HTTP请求的简易指南

- 便携PDF浏览器:随时随地快速查看文档

- VTF格式图片编辑工具:深入起源引擎贴图修改