FPGA设计:关键路径优化与资源共享策略

版权申诉

111 浏览量

更新于2024-08-11

收藏 369KB PDF 举报

FPGA设计技巧专注于优化关键路径以提高设计效率和性能。在FPGA设计中,关键路径是指决定整个电路最短延迟路径,任何延迟变化都可能影响整体时序。为了满足严格的时序约束,设计师需要尽可能减少关键路径上的逻辑单元数量,以降低延迟。

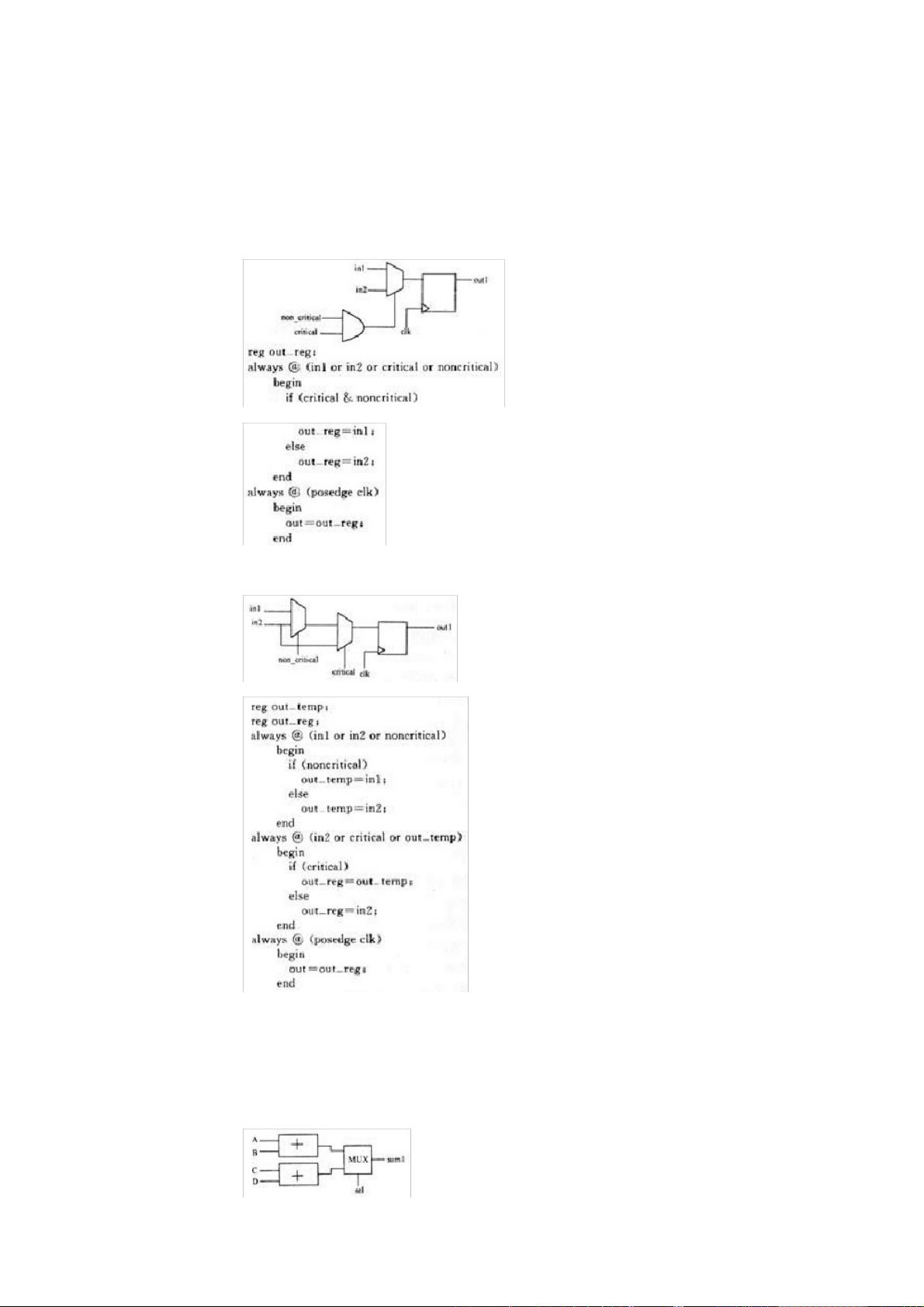

1. 减少逻辑单元:通过精心设计,比如在上述示例中,将原先“critical”经过的2个逻辑单元简化为1个,通过逻辑重组或优化算法,避免不必要的逻辑冗余,从而缩短关键路径的长度。

2. 资源共享:通过模块化和代码重写,使得多个逻辑功能共享相同的硬件资源,如宏单元,以减少硬件占用。例如,一个简单的二选一选择器和加法器可以合并为一个复用的单元,提高资源利用率。

3. 复制逻辑优化:综合工具通常不能完美地布局和布线复杂设计。利用扇出控制,复制逻辑可以在设计中插入重复部分,虽然可能会增加硬件面积,但综合工具可以处理并优化这些复制,提高设计的性能。

4. 组合逻辑复制与触发器优化:对于无法在CLB(基本逻辑单元)内部实现的大扇出组合逻辑,需要进行复制以减小延迟。同时,大扇出触发器的复制可以降低扇出,改善布线,并允许信号驱动芯片的不同区域。通过修改代码实现这些复制操作,可以有效优化设计。

5. 阶层化设计:复杂的电路设计采用层次化方法,将任务分解到可控制的模块中,形成模块化的结构。这种设计方式便于代码维护、继承,以及模块间的高效通信。例如,通过使用寄存器作为模块间边界,有助于提高综合后的电路速度,并减少重复劳动。

FPGA设计中的关键路径优化策略涉及逻辑简化、资源管理和复用、以及针对特定问题的高级设计技术,如复制和层次化结构。通过这些技巧,设计人员可以实现高性能且符合时序约束的FPGA设计。

2020-10-16 上传

2021-07-13 上传

2021-08-11 上传

2021-07-13 上传

2021-07-13 上传

2021-11-09 上传

2021-04-26 上传

2023-04-23 上传

2024-04-01 上传

_webkit

- 粉丝: 30

- 资源: 1万+

最新资源

- 掌握压缩文件管理:2工作.zip文件使用指南

- 易语言动态版置入代码技术解析

- C语言编程实现电脑系统测试工具开发

- Wireshark 64位:全面网络协议分析器,支持Unix和Windows

- QtSingleApplication: 确保单一实例运行的高效库

- 深入了解Go语言的解析器组合器PARC

- Apycula包安装与使用指南

- AkerAutoSetup安装包使用指南

- Arduino Due实现VR耳机的设计与编程

- DependencySwizzler: Xamarin iOS 库实现故事板 UIViewControllers 依赖注入

- Apycula包发布说明与下载指南

- 创建可拖动交互式图表界面的ampersand-touch-charts

- CMake项目入门:创建简单的C++项目

- AksharaJaana-*.*.*.*安装包说明与下载

- Arduino天气时钟项目:源代码及DHT22库文件解析

- MediaPlayer_server:控制媒体播放器的高级服务器