基于EDA技术的VHDL数字秒表设计与实现

需积分: 10 79 浏览量

更新于2024-07-24

收藏 391KB DOC 举报

"数字秒表的设计是一个课程设计项目,涉及到EDA技术和VHDL语言的运用。设计目的是理解并实践计算机电路中的时钟控制系统,学习状态机工作原理,以及掌握时钟脉冲的产生和作用。该秒表能计时0到59分59.99秒,精度为10毫秒,具备复位和启停功能。EDA技术是电子设计自动化的一种工具,用于IC设计、电子电路设计和PCB设计。"

在当前的科技环境中,集成电路和计算机技术的快速发展使得电子设备无处不在。数字秒表作为其中的一个典型应用,其设计和实现涉及到关键的技术领域。本课程设计的核心是通过数字秒表的构建来深化对这些技术的理解。

首先,课程设计的目标包括熟悉EDA实验开发系统,学习和应用EDA技术,这是现代电子设计不可或缺的部分。EDA技术利用计算机辅助设计,通过HDL(硬件描述语言)如VHDL来描述电路行为,实现逻辑编译、优化和仿真,直至生成适合特定芯片的配置。这有助于提高设计效率,降低错误率,尤其在复杂的集成电路设计中。

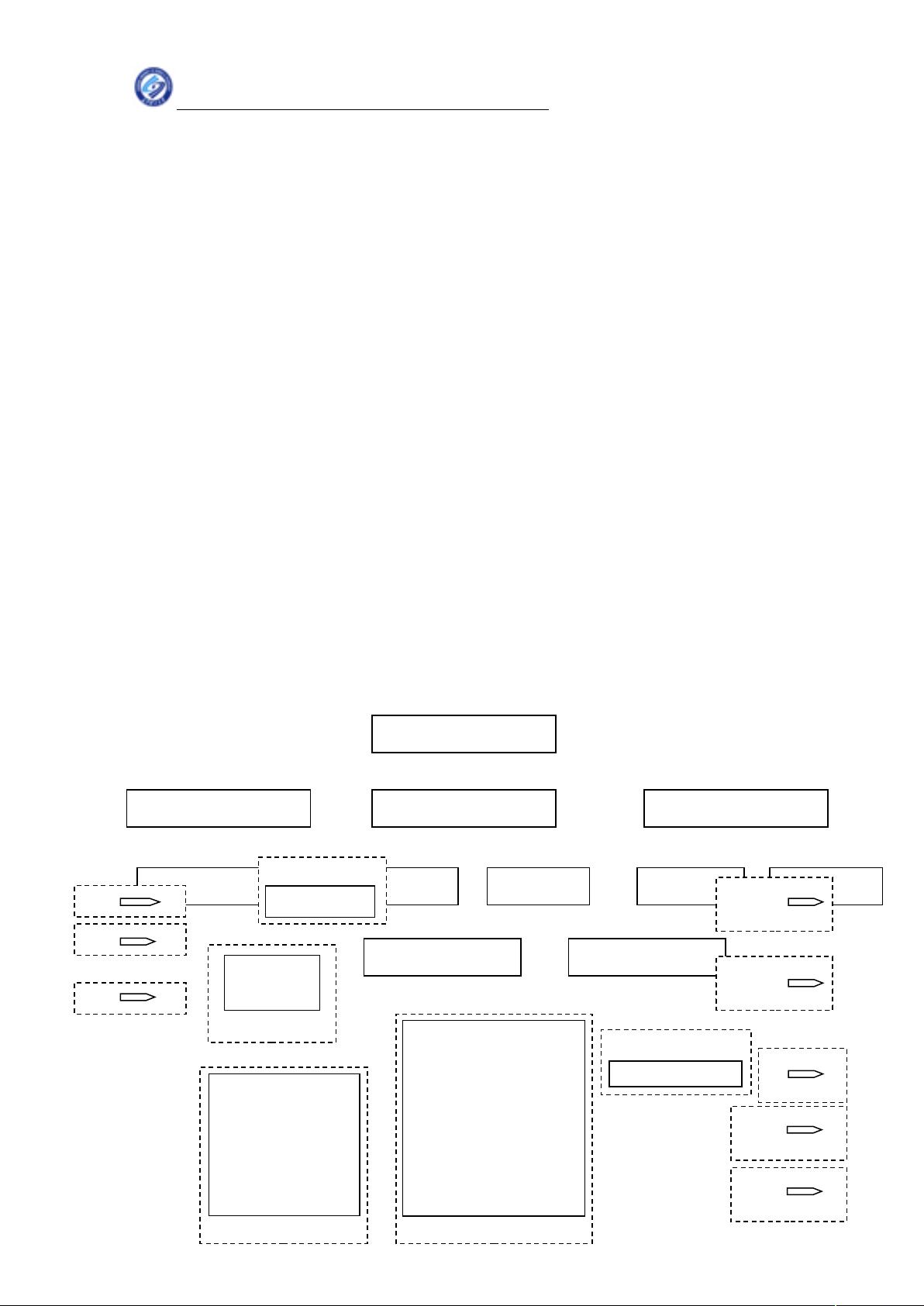

VHDL是硬件描述语言之一,用于描述数字系统的结构和行为。在数字秒表的设计中,VHDL被用来编写控制模块、时基分频模块、计时模块和显示模块的程序。控制模块负责管理秒表的启动、停止和复位操作;时基分频模块则用于生成精确的时间间隔,可能通过分频器将系统时钟脉冲进行分频,以达到10毫秒的计时精度;计时模块负责累加时间,而显示模块则将计时结果转化为可读的数字形式呈现出来。

课程设计的内容还包括实现一个具有复位和启停功能的数字秒表。复位开关允许在任何时间重置计时器,使其回到零状态,而启停开关则控制秒表的运行和暂停,以适应不同场景的需求。

通过这次课程设计,学生能够将理论知识与实践相结合,提升计算机相关的设计和问题解决能力,特别是对计算机结构和控制实现的深入理解。此外,它还强调了在实际工程问题中应用所学知识的重要性,为未来的电子设计和计算机系统开发打下坚实基础。

373 浏览量

342 浏览量

932 浏览量

522 浏览量

280 浏览量

zs2010211251

- 粉丝: 0

- 资源: 25

最新资源

- Community Server专题.pdf

- Vim用户手册,VIM入门好书。

- 华为公司(南京上海)笔试题大全

- 使用.NET和Vss进行团队开发

- Developing J2EE Applications with the UML and Rational Rose

- C#深入浅出全接触和一些基本的介绍

- 单运算放大器,中文版。介绍运放的常用电路。

- 电脑硬盘维修资料(word格式)

- 无线电遥控器的工作原理及红外线原理

- Effcient C++ Programming Techniques

- 轻松搞定 sql server 2000 程序设计.pdf

- Java 多线程编程详解

- MyEclipse 6 Java EE 开发中文手册

- 子网掩码划分 计算机等级考试四级网络工程师

- Keil 与proteus 连接调试

- Ajax for Dummies.pdf