VHDL设计:键盘扫描与计算器实现与仿真

版权申诉

该文档详细介绍了如何通过VHDL进行键盘扫描与计算器的设计与仿真。主要内容包括以下几个部分:

1. 实验目标:

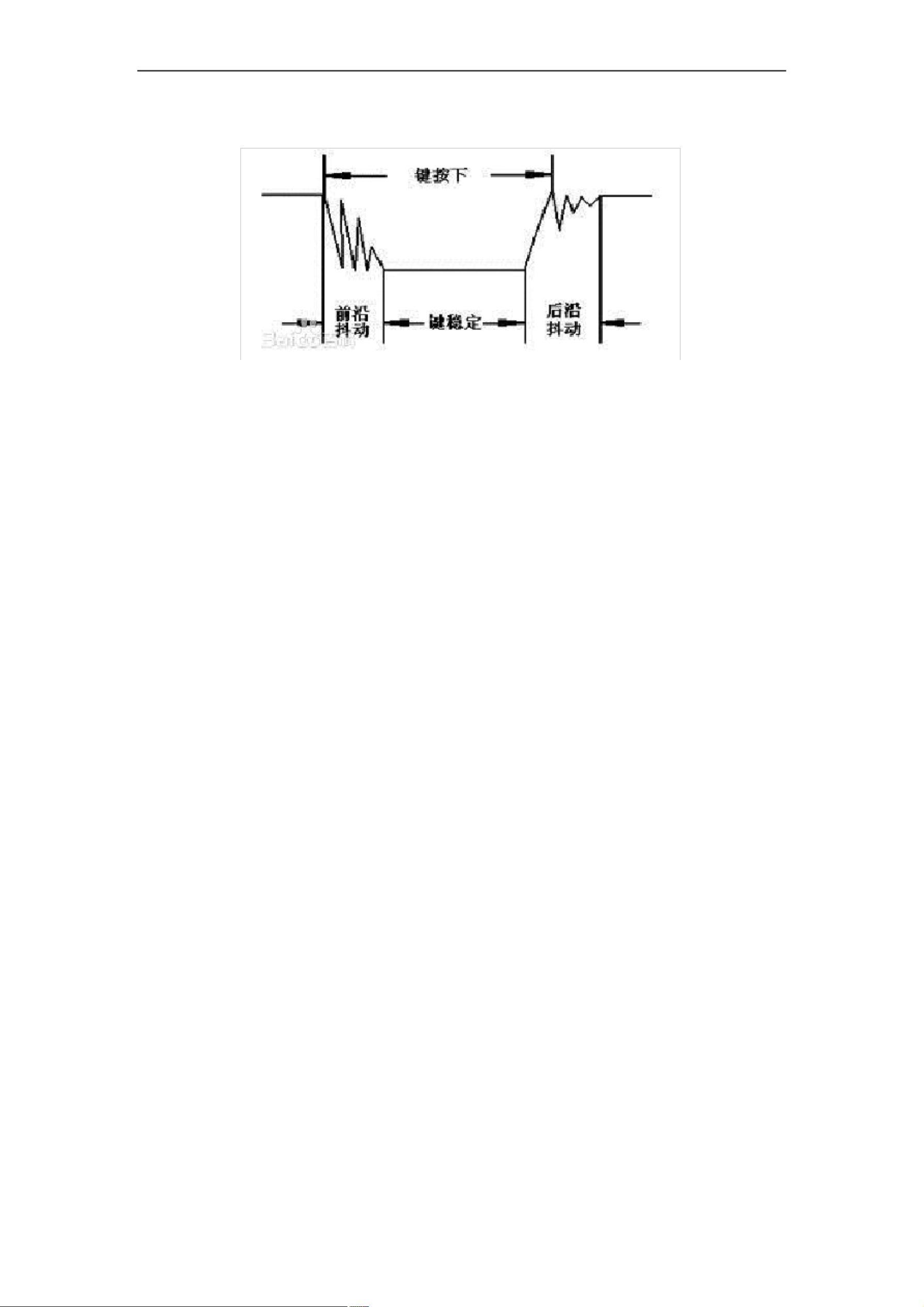

实验要求设计一个能够完成个位数加减乘运算的简易计算器,用户通过矩阵键盘输入,结果显示在数码管上。设计需考虑键盘扫描的实时性和防抖处理,确保每次按键后能正确识别并立即更新显示。

2. 系统组成与连接:

系统由七部分构成,包括分频模块、键盘扫描驱动模块、键盘按键值编码模块、键盘编码值防抖模块、运算模块、数码管显示驱动模块和动态扫描驱动模块。分频模块至关重要,因为它将高频率的系统时钟降频至4KHz和10Hz,分别用于行驱动和防抖处理。

3. 分频模块设计:

利用VHDL中的fredivn组件,通过可变分频技术,将33.8688MHz的时钟源分频,确保键盘扫描和防抖功能的稳定运行。分频元件的参数设定为n=3,实现时钟频率的适当降低。

4. 行驱动模块:

键盘扫描依赖于行信号的快速置零。当按下按键后,对应的列信号会保持为零,从而确定按键的位置。代码中包含了一个计数器来控制行信号的变化,以便快速判断按键。

5. 数码管显示与动态扫描:

计算器的运算结果通过动态扫描显示在数码管上,确保实时更新。这部分涉及到数码管驱动逻辑,以及如何根据运算结果选择合适的显示模式。

6. 仿真结果:

文档提供了实际的仿真结果,显示了分频和键盘扫描功能的工作效果,验证了设计的正确性。这些模拟结果对于理解和评估设计的性能至关重要。

这份VHDL仿真设计文档深入浅出地讲解了如何在FPGA平台上实现键盘扫描与计算器的功能,并通过实例代码展示了关键技术的运用。这对于理解VHDL设计过程和数字逻辑电路实现具有很高的参考价值。

2021-09-30 上传

114 浏览量

202 浏览量

112 浏览量

119 浏览量

a66889999

- 粉丝: 45

最新资源

- Openaea:Unity下开源fanmad-aea游戏开发

- Eclipse中实用的Maven3插件指南

- 批量查询软件发布:轻松掌握搜索引擎下拉关键词

- 《C#技术内幕》源代码解析与学习指南

- Carmon广义切比雪夫滤波器综合与耦合矩阵分析

- C++在MFC框架下实时采集Kinect深度及彩色图像

- 代码研究员的Markdown阅读笔记解析

- 基于TCP/UDP的数据采集与端口监听系统

- 探索CDirDialog:高效的文件路径选择对话框

- PIC24单片机开发全攻略:原理与编程指南

- 实现文字焦点切换特效与滤镜滚动效果的JavaScript代码

- Flask API入门教程:快速设置与运行

- Matlab实现的说话人识别和确认系统

- 全面操作OpenFlight格式的API安装指南

- 基于C++的书店管理系统课程设计与源码解析

- Apache Tomcat 7.0.42版本压缩包发布