ISE IP核使用教程:除法器与CORDIC算法详解

“ISE IP核使用说明”是一份详细的文档,主要介绍了如何在Xilinx的ISE(Integrated Software Environment)集成开发环境中使用IP核。该文档涵盖了多个重要的数字逻辑设计组件,如除法器、CORDIC算法IP核、复数乘法器等,并提供了设置和应用这些IP核的具体步骤。

1. **除法器**:

- **Radix-2与HighRadix类型**:除法器有两种工作模式,Radix-2和HighRadix。Radix-2模式不提供RDY信号,可能需要计数器来检测运算完成,而HighRadix模式提供了RDY和ND握手信号,使得连续除法操作更加方便。

- **补码表示**:在Radix-2模式下,包括符号位在内的小数部分已经补码化,需要特别处理负数情况。例如,当整数部分为负时,需要减一来实现加一的操作。

- **小数最高位判断**:在判断商是否为零时,应关注小数部分的最高位,而非整数部分,因为商为零时,无论小数部分正负,整数部分都会是全零。

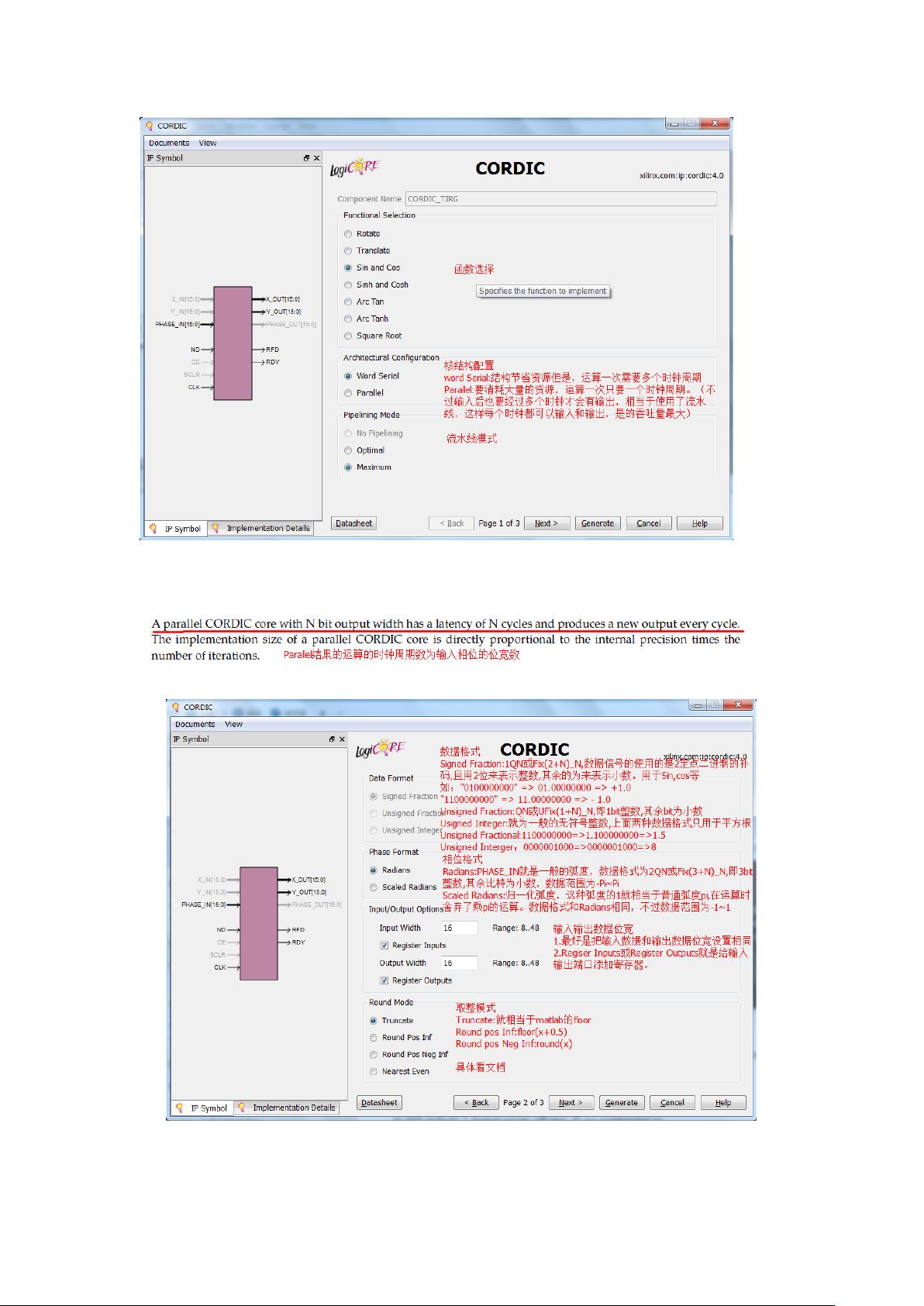

2. **CORDIC**:

- **CORDIC-IP核**:这是一种基于坐标旋转算术的算法,用于执行各种数学运算,如矢量旋转、乘法、除法、对数、指数和三角函数。

- **CORDIC-sin/cos**:这个IP核专门用于计算正弦和余弦值,适用于需要精确角度转换的应用。

- **CORDIC-SQRT**:用于快速计算平方根的IP核,对于需要高效浮点运算的系统非常有用。

3. **其他IP核**:

- **BlockMemory**:用于实现FPGA内部的块存储器,可配置为BRAM或分布式RAM,用于数据存储和缓存。

- **Shift-Register**:移位寄存器IP核用于数据的串行输入和并行输出,或者并行输入和串行输出。

- **ACC累加器**:累加器IP核用于执行累加操作,常见于信号处理和计算密集型应用。

- **复数乘法器**:用于计算复数的乘法,是数字信号处理中的重要组件。

- **乘法器**:基础的乘法IP核,支持不同位宽的乘法操作。

- **FFT**:快速傅里叶变换IP核,用于进行离散傅里叶变换,常用于频谱分析和滤波器设计。

- **FIFO**:先进先出(FIFO)队列,用于实现数据缓冲,保持数据流的同步。

4. **模块信号接口**:

- 每个IP核都有特定的输入和输出信号,例如除法器模块的`DIVdiv`有`clk`输入,表示时钟信号,用于同步IP核的操作。

这份文档对于初学者来说是一份宝贵的资源,因为它详细解释了各个IP核的工作原理和使用方法,有助于理解如何在实际设计中集成和配置这些硬件组件。通过学习这些内容,开发者能够更有效地利用ISE工具创建复杂的数字系统。

2016-11-25 上传

点击了解资源详情

2013-06-20 上传

2011-01-12 上传

2023-06-21 上传

2016-01-08 上传

2011-02-22 上传

zcl_33

- 粉丝: 16

- 资源: 61

最新资源

- Acquisition-4.10-cp310-cp310-manylinux_2_5_x86_64.whl.zip

- my-react-boilerplate:一个简单易用的react + webpack + hot-loader样板用于生产应用程序。 这就是我用的

- WinForms ColorEditor显示无模式

- MEAN-Projects:这些是我已经开发并仍在学习MEAN堆栈的示例项目

- AccessControl-6.0-cp39-manylinux_x86_64.whl.zip

- js实现书架式图片缩放显示效果源码.zip

- 362-用P1口显示红外遥控器的按键值单片机C语言源码.zip项目程序C语言源码下载

- java代码-面积 周长

- 简历模板(可任意修改) (679).zip

- 计算给定公式的真值表-12-静态web服务器-返回指定页面.ev4.rar

- MayaNodeInterface:我设计了这种基于节点的界面,作为学习Python和PyQt的一种方式。 它是与Maya 2011一起开发的,并且(到目前为止)仅与Maya 2011一起使用。它仅适用于设置粒子系统。 某些节点功能尚未完成,但大部分都已完成

- mongodb:MongoDB实践

- js实现的球形放大镜效果源码.zip

- poalab-remodeling

- AccessControl-6.1-cp39-cp39-macosx_11_0_arm64.whl.zip

- java代码-49.陈烁婷