FPGA实战:数码管静态显示原理与设计解析

版权申诉

55 浏览量

更新于2024-08-11

收藏 240KB PDF 举报

"FPGA实战之数码管静态显示的讲解,包括数码管的工作原理、设计思路以及代码实现。"

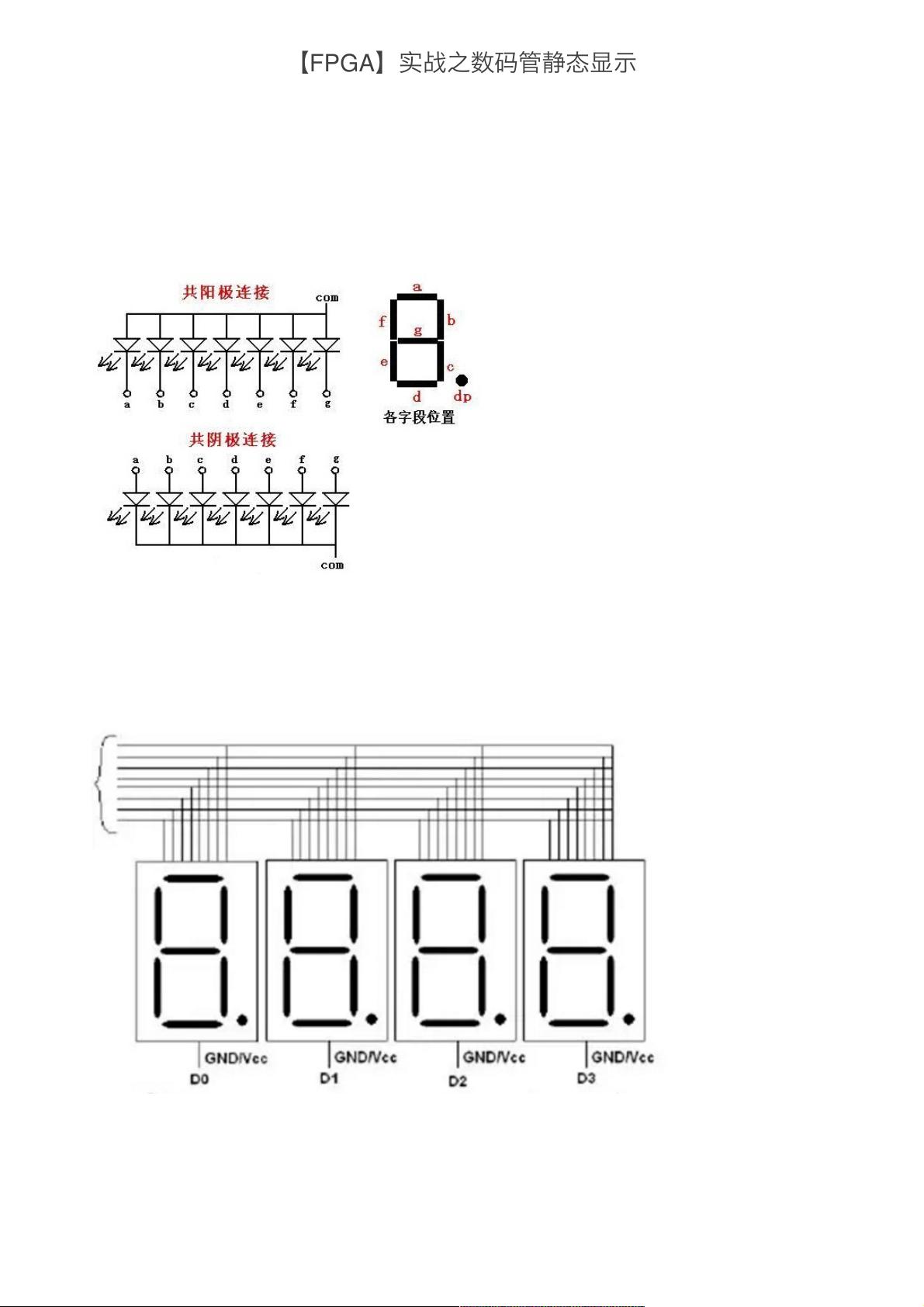

本文档详细介绍了如何使用FPGA进行数码管静态显示的开发。数码管是由8个LED组成,共阳极设计意味着当低电平时LED会亮起。数码管的显示方式分为静态和动态两种。静态显示是指每个数码管的片选和段选都有独立接口,因此所需的接口数量较多,而动态显示则通过快速切换显示不同的数码管来减少接口需求。

在设计思路部分,文档指出一个简单的数码管显示数字任务可以通过高电平直接控制。但在此案例中,任务升级为结合按键和蜂鸣器模块,要求在1小时内完成静态数码管显示的进阶设计。设计的关键在于,按键按下时更新寄存器值,每次按键后数码管的显示随之改变,同时根据情况触发蜂鸣器。这个练习适合初学者,旨在提高对FPGA设计的理解和实践能力。

在代码部分,给出了名为seg.v的数码管静态显示模块。该模块包含输入时钟(clk)、复位信号(rst_n)、两个按键输入(key_down)以及数码管的段选输出(seg_dig)和片选输出(seg_sel)。通过局部参数定义了数码管每个数字的段码。在 always @(posedge clk or negedge rst_n) 语句中,根据复位信号或按键状态更新num寄存器,从而控制数码管的显示。如果按键0被按下,num递增;按键1按下,num递减;若num超过9,则重置回6。

这段代码展示了如何将硬件描述语言(HDL)用于FPGA设计,将逻辑控制与物理显示相结合,体现了FPGA的并行处理能力和实时响应特性。对于学习FPGA开发和数字系统设计的读者来说,这是一个非常实用的例子。

203 浏览量

2023-05-10 上传

2022-06-17 上传

360 浏览量

109 浏览量

2023-07-26 上传

2023-03-14 上传

_webkit

- 粉丝: 31

- 资源: 1万+

最新资源

- StudentManagement:JAVA+MySQL数据库设计完成的学生管理系统,界面使用的Java Swing

- 凡诺企业网站管理系统PHP版-PHP

- Unity独数游戏《sudoku-2017》

- Github-Trending-Repos-Android-App:一个基于Github api的Android应用,可根据创建日期显示趋势仓库

- 重量计算器

- lathe-firmware

- 2016 bctf exploit bcloud 400.rar

- 电脑软件一键禁用WIN10自带更新和杀毒.rar

- Auto Union Type.c Tab-crx插件

- ScreenToGif.2.17.1.Setup.msi

- easyapi:for面向人类的概念验证API生成器

- nodeDatagram

- angular-user-search-github::pencil_selector:简单的Angular-CLi应用程序搜索github用户

- jQuery基于CSS3文字动画特效特效代码

- omnetpp-5.5.1-src-windows.zip

- BabyShop:一个简单的电子商务网站,我们可以在其中租用一些婴儿用品。 有关更多信息,请浏览自述文件